# DOKUZ EYLUL UNIVERSITY GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

# DESIGNING LOCAL DIMMING ALGORITHM FOR HIGH CONTRAST RATIO AND LOW POWER CONSUMPTION FOR LED BACKLIGHT LCD TV SETS

by Yusuf ÖZTÜRK

> October, 2009 İZMİR

# DESIGNING LOCAL DIMMING ALGORITHM FOR HIGH CONTRAST RATIO AND LOW POWER CONSUMPTION FOR LED BACKLIGHT LCD TV SETS

A Thesis submitted to the,

Graduate School of Natural and Applied Sciences of Dokuz Eylul University In

Partial Fulfilment of the Requirements for the Degree Master of Science in

Electric and Electronic Engineering, Electric and Electronic Engineering

Program.

by Yusuf ÖZTÜRK

> October, 2009 İZMİR

# M.Sc THESIS EXAMINATION RESULT FORM

We have read the thesis entitled "DESIGNING LOCAL DIMMING ALGORITHM FOR HIGH CONTRAST RATIO AND LOW POWER CONSUMPTION FOR LED BACKLIGHT LCD TV SETS" completed by YUSUF ÖZTÜRK under supervision of ASST. PROF. DR. ÖZGE ŞAHİN and we certify that in our opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

| Ass           | t. Prof. Dr. Özge ŞAHİN<br>Supervisor |                |

|---------------|---------------------------------------|----------------|

|               |                                       |                |

|               |                                       |                |

|               |                                       |                |

| (Jury Member) |                                       | ( Jury Member) |

|               |                                       |                |

|               |                                       |                |

Director

Graduate School of Natural and Applied Sciences

Prof.Dr. Cahit HELVACI

# **ACKNOWLEDGEMENTS**

I would like to thank Asst. Prof. Dr. Ozge SAHIN for giving me the opportunity of implementing my thesis in this useful area of consumer electronics.

I also would like to thank to TÜBİTAK for its support through my master degree.

I also would like to thank Vestel Electronics and Grundig Electronics for their endless help during my thesis work.

I also would like to thank to my precious wife and my family for their never ending support throughout my life.

Yusuf ÖZTÜRK

# DESIGNING LOCAL DIMMING ALGORITHM FOR HIGH CONTRAST RATIO AND LOW POWER CONSUMPTION FOR LED BACKLIGHT LCD TV SETS

## **ABSTRACT**

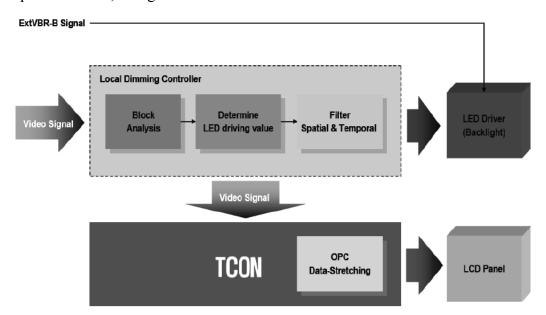

Backlight level of LCD TV with LED backlight unit can be dimmed locally depending on the input video. This feature saves power and increases contrast ratio. Dimming is applied by three ways; zero-dimensional dimming, one-dimensional dimming and two-dimensional dimming. Most popular and effective dimming type is two-dimensional dimming. There are many algorithms to achieve two-dimensional dimming and this thesis brings a novel approach to this issue. The algorithm developed at this study is realized on FPGA chipset and is applied successfully. Algorithm is implemented on 42" full high definition with LED backlight panels and TV sets which have full high definition output. Application uses low voltage differential signalling of TV mainboards and never manipulates image data.

To see the results of the algorithm, three different measurements are taken from the system. Power consumption and contrast ratio are measured for five different images on cold cathode fluorescent lamp backlight, LED backlight and LED backlight with local dimming panels. Measured values have revealed that the algorithm is applied successfully. In terms of contrast ratio, improvement is very high on black-weighted images than white-weighted images. Measurements have emerged that power consumption depends on the white level of the image. It is approved that LED backlight panels, with local dimming or not, are better than cold cathode fluorescent lamp backlight panels in terms of both power consumption and contrast ratio.

**Keywords**: Local dimming, LED backlight panel, Dimming algorithm, Contrast ratio, Power consumption.

# LED ARKA IŞIKLI TELEVİZYON ÜNİTELERİ İÇİN GÜÇ TÜKETİMİNİ AZALTICI VE KOTRAST ORANINI ARTRICI YEREL KISMA ALGORİTMASI GELİŞTİRİLMESİ

ÖZ

Sıvı Kristal Ekran Televizyonun arka ışık seviyesini yerel olarak giriş video sinyaline göre kısma işlemi yapılabilir. Bu, güç tüketimini azalmak ve kontrast oranını arttırmaktadır. Boyutsuz, bir boyutlu ve iki boyutlu olmak üzere üç farklı tür kısma işlemi alternatifi mevcuttur. LED arka ışıklı paneller için en çok tercih edileni iki boyutlu kısma işlemidir. İki boyutlu kısma işlemi için çeşitli algoritmalar geliştirilmiştir. Bu tezde de iki boyutlu yerel kısma işlemi için algoritma tasarlanmıştır. Tasarlanan algoritma alan programlamalı kapı dizisi üzerinde gerçekleştirilmiş ve başarıyla uygulanmıştır. Algoritma, tam yüksek çözünürlüklü LED arka ışıklı 42 inç panel kullanılarak gerçeklenmiş ve tam yüksek çözünürlüklü tüm platformlarda çalışabilecek şekilde tasarlanmıştır. Uygulama, anakartların düşük gerilim fark sinyalleri kullanılarak, orijinal sinyaller değiştirilmeden gerçeklenmiştir.

Algoritmanın sonuçlarını görmek için 3 farklı sistem için ölçüm alınmıştır. Soğuk katot floresan lamba arka aydınlatmalı, LED arka aydınlatmalı ve yerel ayarlanabilen LED arka aydınlamalı panellerde 5 farklı resim için güç tüketimi ve kontrast oranları ölçülmüştür. Ölçüm değerleri algoritmanın başarılı bir şekilde uygulandığını ortaya koymuştur. Kontrast oranı olarak siyah ağırlıklı resimlerde kontrast oranı çok yüksek çıkarken beyaz ağırlıklı resimlerde kontrast oranı bakımından iyileşme çok yüksek olmamıştır. Güç tüketiminin ise beyaz seviyesine göre değiştiği ölçüm sonuçlarından ortaya çıkmıştır. LED arka aydınlatmalı panellerin yerel kısma olmaksızın soğuk katot floresant lamba arka aydınlatmalı panellere göre hem kontrast oranı hem de güç tüketimi açısından avantajlı olduğu gösterilmiştir.

**Anahtar Sözcükler**: Yerel Ayarlama, LED Arka Işıklı panel, Kısma algoritması, Kontrast oranı, güç tüketimi.

# **CONTENTS**

|                                            | Page      |

|--------------------------------------------|-----------|

| M.Sc THESIS EXAMINATION RESULT FORM        | ii        |

| ACKNOWLEDGEMENTS                           | iii       |

| ABSTRACT                                   | iv        |

| ÖZ                                         | V         |

| CHAPTER ONE - INTRODUCTION                 | 1         |

| CHAPTER TWO - DISPLAY AND BACKLIGHT TECHNO | OLOGIES 4 |

| 2.1 Cathode Ray Tube (CRT)                 | 5         |

| 2.2 Plasma Display Panel (PDP)             | 9         |

| 2.3 Liquid Crystal Display LCD             | 12        |

| 2.3.1 Liquid Crystals                      | 13        |

| 2.3.2 Liquid Crystal Display Basics        | 13        |

| 2.3.2.1 The Liquid Crystal Cell            | 14        |

| 2.3.4 Liquid Crystal Display Types         | 16        |

| 2.4 Organic Light Emitting Diodes (OLEDs)  | 19        |

| 2.4.1 Fundamentals of OLEDs                | 20        |

| 2.4.2 Structure and Types of OLEDs         | 20        |

| 2.4.4 OLED Benefits                        | 22        |

| 2.5 Digital Light Processing (DLP)         | 22        |

| 2.5.1 DLP Structure                        | 23        |

| 2.5.2 DLP in Color                         | 23        |

| 2.5.3 DLP Uses                                | 23 |

|-----------------------------------------------|----|

| 2.6 Field Emission Displays (FEDs)            | 24 |

| 2.6.1 Field Emission Fundamentals             | 24 |

| 2.6.2 Traditional FED Structure               | 26 |

| 2.7 Backlight Technologies                    | 26 |

| 2.7.1 Cold Cathode Fluorescent Lamp (CCFL)    | 27 |

| 2.7.1 Light Emitting Diodes (LED)             | 28 |

| 2.7.2.1 Advantages of LEDs                    | 29 |

| 2.7.2.2 Disadvantage of LEDs                  | 30 |

| 2.7.3 Electroluminescent Panel (ELP)          | 30 |

| CHAPTER THREE - FIELD PROGRAMMABLE GATE ARRAY | 32 |

| 3.1 Introduction                              | 32 |

| 3.2 Modern Developments                       | 33 |

| 3.2.1 Gates                                   | 34 |

| 3.2.2 Market Size                             | 34 |

| 3.2.3 FPGA Design                             | 35 |

| 3.3 FPGA Comparisons                          | 35 |

| 3.4 FPGA Architecture                         | 36 |

| 4.4 FPGA Design and Programming               | 40 |

| 4.5 Which FPGA is Chosen For This Project     | 41 |

| CHAPTER FOUR - LOCAL DIMMING APPLICATION      | 42 |

| 4.1 Technical Information                     | 42 |

| 4.1.1 LED Backlight Unit and Its Types               | 42 |

|------------------------------------------------------|----|

| 4.1.1.1 LED Overview                                 | 42 |

| 4.1.2 Contrast Ratio                                 | 44 |

| 4.1.2.1 Methods of Contrast Ratio Measurements       | 45 |

| 4.1.2.2 Dynamic Contrast Ratio                       |    |

| 4.2 Software Design                                  |    |

| 4.2.1 Definition of the Design Method                | 48 |

| 4.2.1.1 Video Signal                                 | 48 |

| 4.2.1.2 Block Analysis                               |    |

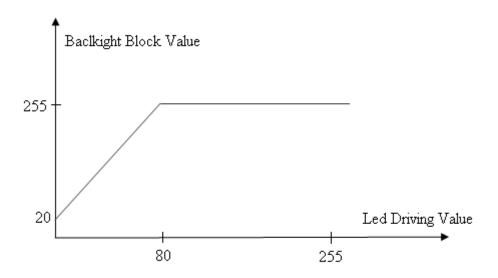

| 4.2.1.3 Determine LED Block Driving Value            | 50 |

| 4.2.1.4 Spatial Filtering                            | 52 |

| 4.2.1.5 Temporal Filtering                           | 53 |

| 4.2.1.6 Driving LED Blocks                           | 53 |

| 4.2.2 Algorithm                                      | 54 |

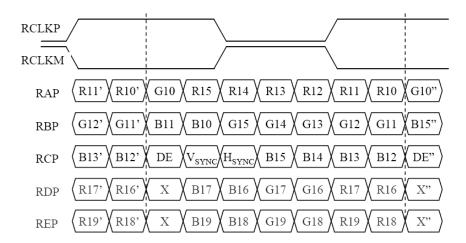

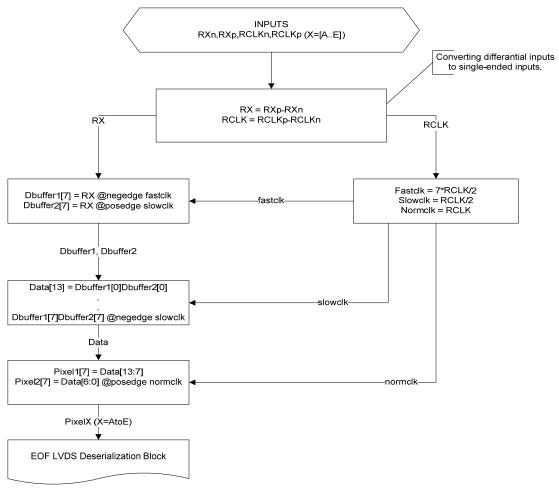

| 4.2.2.1 Algorithm of De-serialization Block          | 54 |

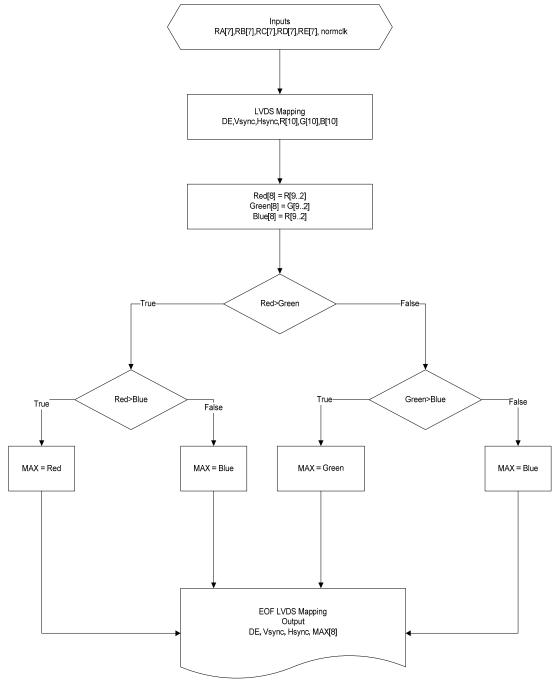

| 4.2.2.2 Algorithm of LVDS Mapping                    | 56 |

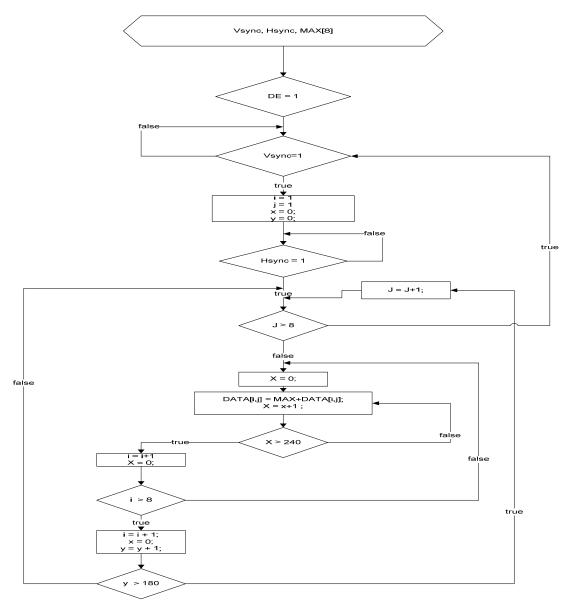

| 4.2.2.3 Algorithm of Dimming Value Calculation Block | 57 |

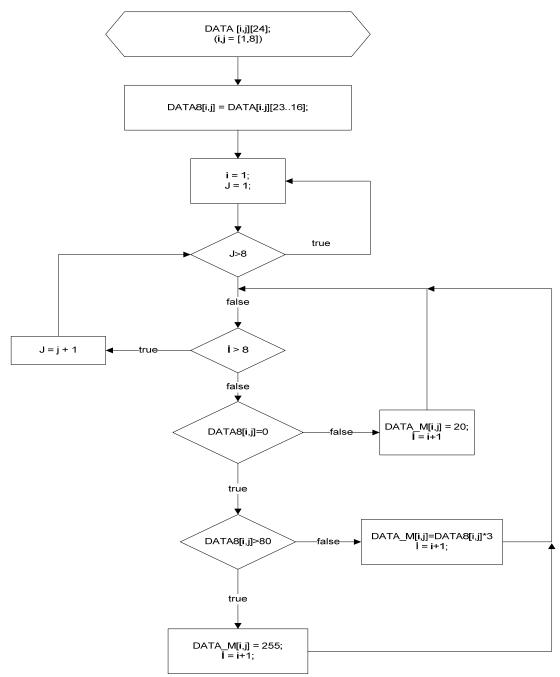

| 4.2.2.4 Algorithm of Data Mapping Block              | 57 |

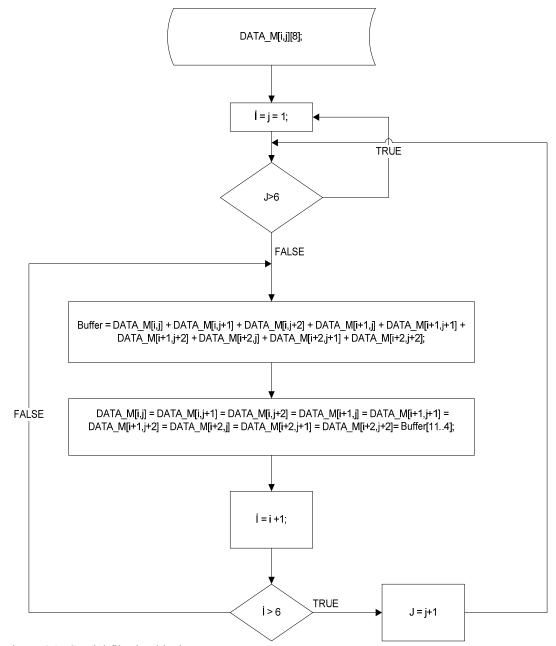

| 4.2.2.5 Algorithm of Spatial Filtering Block         | 58 |

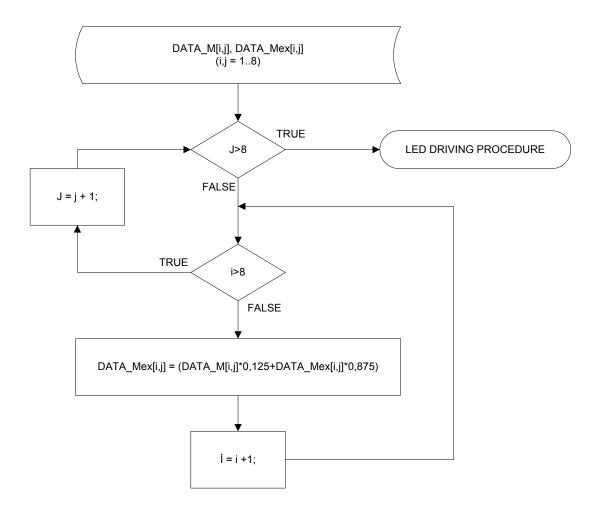

| 4.2.2.6 Algorithm of Temporal Filtering Block        | 59 |

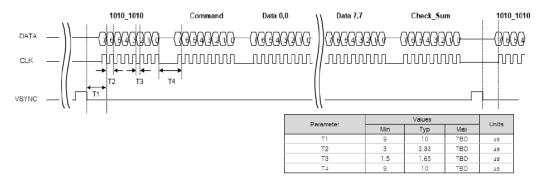

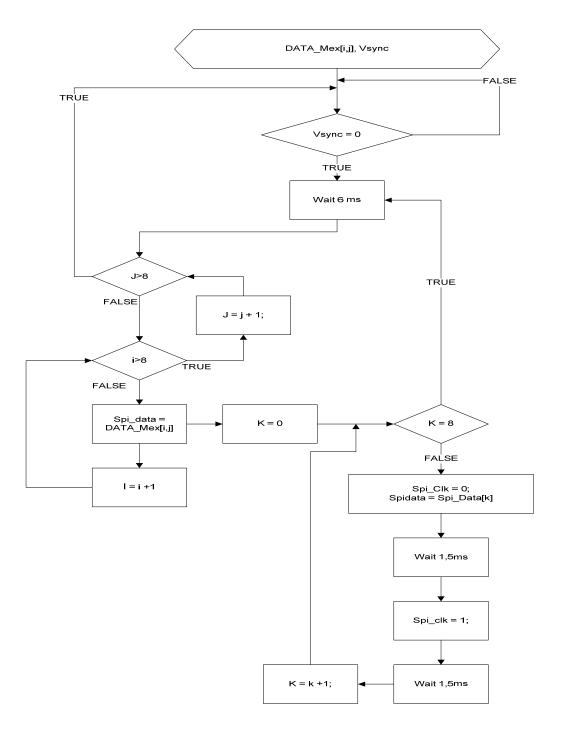

| 4.2.2.7 Algorithm of SPI Data Generation Block       | 60 |

| 4.2.3 Hardware Structure                             | 62 |

| CHAPTER FIVE- RESULTS                                | 64 |

| CHAPTER SIX - CONCLUSION                             | 70 |

| REFERENCES                                           | 73 |

| APPENDICES                                           | 75 |

| Appendix A Verilog Codes Of Doubling Data            | . 75 |

|------------------------------------------------------|------|

| Appendix B Verilod Codes of Shift Register           | . 76 |

| Appendix C Verilog Codes of Parallel Register        | . 77 |

| Appendix D Verilog Codes of Aligner                  | . 78 |

| Appendix E Verilog Codes of LVDS Mapping             | . 79 |

| Appendix F Verilog Codes of Generating Dimming Value | . 83 |

| Appendix G Verilog Codes of Mapping Dimming Data     | . 85 |

| Appendix H Verilog Codes of Spatial Filtering        | . 87 |

| Appendix I Temporal Filtering                        | . 89 |

| Appendix J Verilog Codes of SPI Data Sending         | . 90 |

| Appendix K Brief datasheet of FPGA                   | . 95 |

| Appendix L Datasheet of Panel                        | . 97 |

| Appendix M LVDS Data Mapping                         | . 99 |

|                                                      |      |

# **CHAPTER ONE**

# **INTRODUCTION**

Today, LCDs are the most common display technology for small (mobile), medium (monitor), and large (TV) display sizes. The image quality equals or exceeds that of a conventional CRT on many front-of-screen parameters, such as color, brightness, and resolution. In terms of contrast and viewing angle, however, an LCD's performance is rather poor. This is caused by the leakage of light from the backlight through the panel when it is in the black state. (Langendijk et al., 2008)

For a dark image, the contrast can be improved significantly by dimming the backlight and simultaneously increasing the drive values to the panel accordingly. (Langendijk et al., 2008)

The process of changing backlight globally, this is called 0D dimming. In this way, backlight should always provide adequate light to depict a scene, because of that, increasing contrast ratio by this method is not effective.

Increasing CR can be accomplished by changing backlights according to the video content. De Greef et al., (2006) presented a lamp-based approach in which each HCFL lamp could be driven independently. This method gives chance to modulate backlight vertically, called 1D dimming.

After developments of LED backlight LCD panels, two dimensional dimming as known 2D dimming come up. Backlight parts of this kind of panels have matrix structure and are addressable individually.

As a result of 2D dimming, dynamic contrast ratios of these sets are very high. Dynamic contrast ratio is division of brightness of full white and brightness of full black. It is known that individual LED backlight blocks are capable of turning off. So

this ratio goes to infinite and cannot be measured. In practical, when full black pattern applied to TV, there exists an offset value for measuring and avoid of artifacts. Dynamic contrast ratio does not mean anything to user.

Static contrast ratio gives information about the scene. As distinct from its name, the ratio cannot be static, changes dynamically according to the scene. In this paper, an algorithm developed and applied for increasing static contrast ratio.

In literature, there are similar studies on this issue. Shiga et al., (2008), work on power savings by changing backlight unit via controlling TV signal at and Langendijk et al., (2008) works on increasing contrast gain and power saving with local dimming. Conclusion of these studies, local dimming saves power and increase contrast ratio and there must be a local dimming algorithm to prove this facts. This thesis aim is to develop a local dimming algorithm and show that power saving and difference at contrast ratio. At these studies, LED backlight panel is not used. One of the differences of this thesis is using LED backlight panel.

The thesis contains 6 chapters. First chapter is introduction. The aim of the thesis is explained in this chapter generally.

In second chapter, detailed explanations of display technologies and backlight technologies can be read. Every type of displays and backlights are explained from historical development to how it works.

FPGA basics are mentioned in chapter three. Basic information, architectures, historical development and why FPGA is chosen are shown at this chapter.

Technical explanations which are used in the thesis are given in chapter four. This chapter contains application part of the thesis. Software design section located at this chapter also. This section tells how the software will be applied. Algorithm schematics can be seen at chapter four.

At chapter five the measurement results take part. The measurement tools and patterns will be shown. For each pattern there are two different measurements will be performed at three setups. One of them is full HD 100Hz LCD TV with local dimming, other one is as same as first one except local dimming, the last setup is Full High Definition (HD) 100Hz Liquid Crystal Display TV with Cold Cathode Fluorescent Lamp (CCFL) backlight.

Chapter six is conclusion part of thesis. According to the results, the achievement of the algorithm will be discussed at this chapter.

# **CHAPTER TWO**

# DISPLAY AND BACKLIGHT TECHNOLOGIES

Display technology has a critical role explaining how information is transmitted. It is better to describe something by a picture than a thousand words, therefore display technology simplifies information sharing. Cathode Ray Tube (CRT) technology has dominated the display industry from 1922 until the late 20th century. However, new trends such as the desire for mobile electronics have increased demand for displays that rival and surpass CRTs in areas such as picture quality, size, and power consumption. One of the latest devices likely to replace CRTs is Liquid Crystal Displays (LCD) depending on their lightweight, low power consumption and design compactness. LCDs allowed devices such as digital watches, cell phones, laptops, and any small screened electronics to be possible. Although LCDs were initially created for handheld and portable devices, they have expanded into areas previously monopolized by CRTs such as computer monitors and televisions. Other contenders for leadership in display technology are Organic LEDs, DLP technology, Plasma Displays, Field Emission Displays, and Electronic Paper. Organic LEDs, being composed of light emitting polymers, can emit their own light to offer thin and power-saving displays. Using many microscopic mirrors, DLP technology can generate large bright projections on screens with up to 35 trillion colors. Plasma Displays generate excellent quality images on very large screens. Field Emission Displays can produce high resolution images like CRTs without the bulky appearance. The makers of Electronic Paper are trying to replace print by developing displays with many paper-like properties. (Gurski & Quach, 2005, p.3)

# 2.1 Cathode Ray Tube (CRT)

The earliest version of the CRT was invented by the German physicist Ferdinand Braun in 1897 and is also known as the 'Braun tube'. (Discover in Medicines Co., 2009) It was a cold-cathode diode, a modification of the Crookes tube with a phosphor-coated screen. The first version to use a hot cathode was developed by John B. Johnson (who gave his name to the term Johnson noise) and Harry Weiner Weinhart of Western Electric, and became a commercial product in 1922.

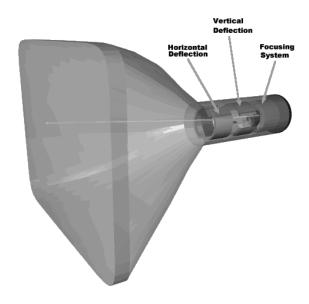

The cathode rays are now known to be a beam of electrons emitted from a heated cathode inside a vacuum tube and accelerated by a potential difference between this cathode and an anode. The screen is covered with a crystalline phosphorescent coating (doped with transition metals or rare earth elements), which emits visible light when excited by high-energy electrons. The beam (or beams, in color CRTs) is deflected either by a magnetic or an electric field to move the bright dot(s) to the required position on the screen. External electromagnets deflect the beams magnetically, while internal plates placed near to and alongside the beam deflect it electrostatically. (Electrostatic deflection is used only for single-beam tubes.)

In television sets and computer monitors the entire front area of the tube is scanned repetitively and systematically in a fixed pattern called a *raster*. A raster is a rectangular array of closely-spaced parallel lines, scanned one at a time, from left to right (and, ever so slightly, "downhill", because the beam is moving steadily down while drawing the image frame). An image is produced by modulating the intensity of each of the three electron beams, one for each primary color (red, green, and blue) with a received video signal (or another signal derived from it). In all CRT TV receivers except some very early models (The earliest commercial TV receivers used electrostatic deflection, even by the end of the 1940s, many of them relying on the famous 7JP4), the beam is deflected by magnetic deflection, a varying magnetic field generated by coils (the deflection yoke), driven by electronic circuits, around the neck of the tube.

Figure 2.1 Electron gun. (Wikimedia Foundation Inc., 2004)

The source of the electron beam is the electron gun, which produces a stream of electrons through thermionic emission, and focuses it into a thin beam. Electron gun can be seen at Figure 2.1. Earlier, black-and-white TV CRTs used magnetic focusing, but electrostatic focus has totally superseded focus coils. The gun is located in the narrow, cylindrical neck at the extreme rear of a CRT and has electrical connecting pins, usually arranged in a circular configuration, extending from its end. These pins provide external connections to the cathode, to various grid elements in the gun used to focus and modulate the beam, and, in electrostatic deflection CRTs, to the deflection plates. Since the CRT is a hot-cathode device, these pins also provide connections to one or more filament heaters within the electron gun. When a CRT is operating, the heaters can often be seen glowing orange through the glass walls of the CRT neck. The need for these heaters to 'warm up' causes a delay between the time that a CRT is first turned on, and the time that a display becomes visible. In older tubes, this could take fifteen seconds or more; modern CRT displays have faststarting circuits which produce an image within about two seconds, using either briefly increased heater current or elevated cathode voltage. Once the CRT has warmed up, the heaters stay on continuously. The electrodes are often covered with a black layer, a patented process used by all major CRT manufacturers to improve electron density. (Wikimedia Foundation Inc., 2004)

The electron gun accelerates not only electrons but also ions present in the imperfect vacuum (some of which result from outgassing of the internal tube components). The ions, being much heavier than electrons, are deflected much less by the magnetic or electrostatic fields used to position the electron beam. Ions striking the screen damage it; to prevent this the electron gun can be positioned slightly off the axis of the tube so that the ions strike the inside of the CRT neck instead of the screen. Permanent magnets (the *ion trap*) deflect the lighter electrons so that they strike the screen. Some very old TV sets without an ion trap show

browning of the center of the screen, known as ion burn. The aluminum coating used in later CRTs eliminated the need for ion traps; they are no longer used.

When electrons strike the poorly-conductive phosphor layer on the glass CRT, it becomes electrically charged, and tends to repel electrons, reducing brightness (this effect is known as "sticking"). To prevent this, the interior side of the phosphor layer can be covered with a layer of aluminum connected to the conductive layer inside the tube, which disposes of this charge. It has the additional advantages of increasing brightness by reflecting, towards the viewer, the light emitted towards the back of the tube. The aluminum layer also protects the phosphors from ion bombardment.

CRTs were embraced as output devices very early in the development of digital computers. There close cousins, vacuum tubes, were some of the first switching elements used to build computers. Today, the CRT is the last remaining vacuum tube in most systems (Even the flashing lights are solid-state LEDs). Structure of CRT display can be seen at Figure 2.2.

Most likely, oscilloscopes were some of the first computer graphics displays. The results of computations could be used to directly drive the vertical and horizontal displacement plates in order to draw lines on the CRT's face. By varying the current to the heating filament the output of the electron beam could also be controlled. This allowed the intensity of the lines to vary from bright to completely dark.

Color CRT's are more complicated than the simple monochrome models summarized above. The phosphors on the face of a color CRT are laid out in a precise geometric pattern. There are two primary variations, the *stripe* pattern of inline tubes shown on the left, and the *delta* pattern of delta tubes as shown on the right.

Within the neck of the CRT there are three electron guns, one each for red, green, and blue (the actual beams are all the same color-- *invisible*). There is also a special metal plate just behind the phosphor cover front face, called a *shadow mask*. This mask is aligned so that it simultaneously allows each electron beam to see only the phosphors of its assigned color and blocks the phosphor of the remaining two colors.

Despite the rapid rise of display solutions based on various flat screen technologies, CRT displays are still in the market and new products are being launched. Arguably, CRT technology continues to offer a superior quality of picture and higher contrast ratios than FPDs and at highly competitive costs (although see the discussion of total cost of ownership when power consumption is considered) and it is likely that CRT will continue to dominate the very low end of the TV market for some time. They are also challenging the 'thinness' issue. Samsung recently announced plans to produce a CRT 32-inch TV display with a depth that is half that of existing solutions. (Discover in Medicines Co., 2007)

Figure 2.2 Structure of CRT

# 2.2 Plasma Display Panel (PDP)

By definition, plasma is a state of matter (gas) where atoms are ionized by adding energy - in this case electrical energy by applying a voltage between two electrodes and which eventually leads to the flow of an electric current. In the process, positive and negative charged particles move fast towards the respectively opposite charged electrodes.

The photon is that elementary particle responsible for all electromagnetic phenomena; it carries electromagnetic radiation - from gamma to radio. If it falls within the light spectrum, visible or otherwise - it is called a light photon.

The released light photons are in effect ultraviolet photons - meaning that the emitted radiation is invisible to the human eye. Ultraviolet light photons can be used to produce visible light by exciting phosphor atoms. Phosphors are substances that give off visible light photons when their atoms are hit by ultraviolet photons. The collision causes electrons to jump to a higher energy level - which energy is then released in the form of a visible light photon when the electron returns to its normal energy level. Different phosphor formulations yield different colors of light. (Wikimedia Foundation Inc., 2005)

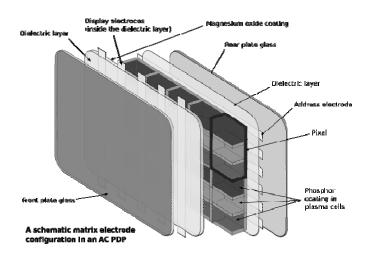

A plasma display panel (PDP) is a type of flat panel display common to large TV displays (32 inches or larger). Many tiny cells between two panels of glass hold an inert mixture of noble gases. The gas in the cells is electrically turned into plasma which then excites phosphors to emit light. Plasma displays should not be confused with LCDs, another lightweight flat screen display using different technology.

Plasma displays are bright (1000 lux or higher for the module), have a wide color gamut, and can be produced in fairly large sizes, up to 381 cm (150 inches) diagonally. They have a very low-luminance "dark-room" black level compared to the lighter grey of the unilluminated parts of an LCD screen. The display panel is

only about 6 cm (2.5 inches) thick, while the total thickness, including electronics, is less than 10 cm (4 inches). Plasma displays use as much power per square meter as a CRT or an AMLCD television. Power consumption varies greatly with picture content, with bright scenes drawing significantly more power than darker ones, as is also true of CRTs. Nominal power rating is typically 400 watts for a 50-inch (127 cm) screen. Post-2006 models consume 220 to 310 watts for a 50-inch (127 cm) display when set to cinema mode. Most screens are set to 'shop' mode by default, which draws at least twice the power (around 500-700 watts) of a 'home' setting of less extreme brightness.

The lifetime of the latest generation of plasma displays is estimated at 100,000 hours of actual display time, or 27 years at 10 hours per day. This is the estimated time over which maximum picture brightness degrades to half the original value, not catastrophic failure.

Plasma displays also have their drawbacks. They are often criticized for reflecting more ambient light than LCD displays. The screen is made from glass, which reflects more light than the material used to make an LCD screen, which creates a glare. Although companies, such as Panasonic, coat their newer plasma screens with an anti-glare filter. Plasma panels currently cannot be made in screen sizes smaller than 32". Although few companies have been able to make plasma EDTVs this small, even fewer have made 32" plasma HDTVs. The 32" screen size is also "going extinct". Plasma displays are also considered bulky and thick (usually six inches in depth) compared to their LCD counterparts. Panasonic aims to solve the thickness issue by releasing the Viera Z1 series, which are only one inch thick. Plasma displays also tend to consume more electricity than LCD displays. Panasonic, once again aims to solve this dilemma by using Neo-PDP screens for their 2009 series of Vieras. Panasonic states that the PDPs will consume half the power to achieve the same overall brightness.

Competing displays include the CRT, OLED, AMLCD, DLP, SED-TV, and field emission flat panel displays. Advantages of plasma display technology are that a large, very thin screen can be produced, and that the image is very bright and has a

wide viewing angle. The viewing angle characteristics of plasma displays and flatface CRTs are essentially the same, topping all LCD displays, which have a reduced viewing angle in at least one direction. Plasma TVs also do not exhibit an image blur common in many LCD TVs.

The xenon, neon, and argon gas in a plasma television is contained in hundreds of thousands of tiny cells positioned between two plates of glass. Long electrodes are also put together between the glass plates, in front of and behind the cells. The address electrodes sit behind the cells, along the rear glass plate. The transparent display electrodes, which are surrounded by an insulating dielectric material and covered by a magnesium oxide protective layer, are mounted in front of the cell, along the front glass plate. Control circuitry charges the electrodes that cross paths at a cell, creating a voltage difference between front and back and causing the gas to ionize and form plasma. As the gas ions rush to the electrodes and collide, photons are emitted.

In a monochrome plasma panel, the ionizing state can be maintained by applying a low-level voltage between all the horizontal and vertical electrodes – even after the ionizing voltage is removed. To erase a cell all voltage is removed from a pair of electrodes. This type of panel has inherent memory and does not use phosphors. A small amount of nitrogen is added to the neon to increase hysteresis.

In color panels, the back of each cell is coated with a phosphor. The ultraviolet photons emitted by the plasma excite these phosphors to give off colored light. The operation of each cell is thus comparable to that of a fluorescent lamp.

Every pixel is made up of three separate sub-pixel cells, each with different colored phosphors. One sub-pixel has a red light phosphor, one sub-pixel has a green light phosphor and one sub-pixel has a blue light phosphor. These colors blend together to create the overall color of the pixel, the same as a "triad" of a shadow-mask CRT or color LCD. By varying the pulses of current flowing through the different cells thousands of times per second, the control system can increase or decrease the intensity of each subpixel color to create billions of different combinations of red, green and blue. In this way, the control system can produce

most of the visible colors. Plasma displays use the same phosphors as CRTs, which accounts for the extremely accurate color reproduction when viewing television or computer video images (which use an RGB color system designed for CRT display technology.) Structure of plasma panel is shown at Figure 2.3.

Figure 2.3 Structure of plasma panel (Wikimedia Foundation Inc., 2005)

# 2.3 Liquid Crystal Display LCD

Liquid crystals were discovered in 1888, but their potential application in display technology was not realized until 1968 when researchers from the RCA's David Sarnoff Research Center developed the first liquid crystal display. Since then, LCDs have revolutionized the small screen and portable electronic market offering an alternative to CRTs and making devices like calculators, cell phones, PDAs, and laptops possible. As LCD designs advance, they will remain a popular part of home entertainment systems and continue to dominate handheld electronics.

# 2.3.1 Liquid Crystals

An Austrian botanist by the name of Friedrich Reinitzer was the first person to perform research on liquid crystals. In 1888 he conducted an experiment involving a material known as cholesterly benzoate. In his experiment Reinitzer observed changes in a solid sample of cholesterly benzoate as he increased the applied temperature. He noticed that as the temperature increased the solid sample became a hazy liquid and then changed into a transparent liquid. A physics professor named Otto Lehmann having learned of Reinitzer's discovery conducted his own research confirming that the substance seem to have two distinct melting points; his research led him in 1889 to coin the term 'liquid crystal'.

Liquid crystals are substances that exhibit properties of both solids and liquids; they are an intermediate phase of matter. Liquid crystals can be classified into three different groups, nematic, smectic, and cholestric depending on the level of order in their molecular structure. Liquid crystals in the nematic group are most commonly used in LCD production because of their physical properties and wide temperature range. In the nematic phase, liquid crystal molecules are oriented on average along a particular direction. By applying an electric or magnetic field, the orientation of the molecules can be manipulated in a predictable manner; this mechanism provides the basis for LCDs. (Gurski & Quach, 2005)

# 2.3.2 Liquid Crystal Display Basics

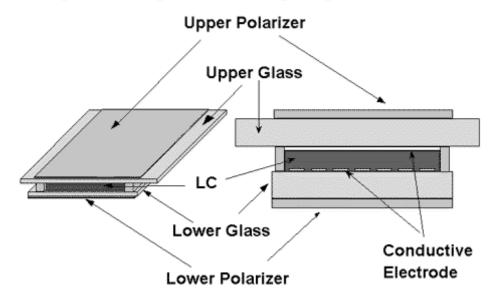

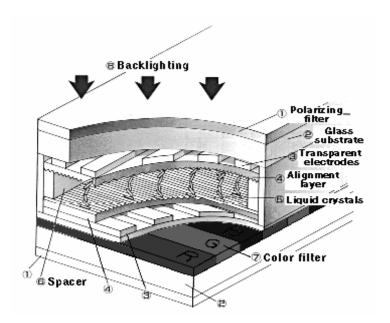

Simple LCDs consist of a liquid crystal cell, conductive electrodes and a set of polarizing lenses. The structure for a simple LCD is shown in the diagram below at Figure 2.4.

# Liquid Crystal Display Structure

Figure 2.4 Basic diagram of an LCD. (Gurski & Quach, 2005)

# 2.3.2.1 The Liquid Crystal Cell

To use liquid crystals in display technology, the ability to control how their molecules are naturally arranged is needed. In their natural state, liquid crystal molecules in the nematic phase are loosely ordered with their long axes parallel; to change this arrangement they are placed onto a finely grooved surface. When they come into contact with a finely grooved surface also called the alignment layer, the molecules line up parallel along the grooves.

Figure 2.5 Molecules near each plate line up in respected directions. (Morris, 1993)

Figure 2.5 shows the directions of molecules. Light sent through the twisted liquid crystal structure curls following the molecular arrangement and figured at Figure 2.6. By changing the orientation of the liquid crystals, light propagating through is also changes to follow.

Figure 2.6 Light rotates following the molecular arrangement. (Morris, 1993)

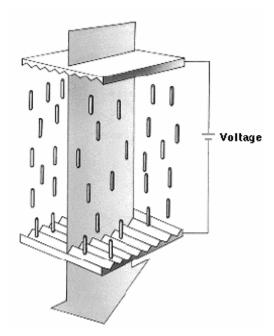

Conductive electrodes are used to apply voltage to the liquid crystal cell as shown at Figure 2.7. When a voltage is applied the molecules straighten out aligning parallel to the applied electric field; this also allows propagating light to pass directly through.

Figure 2.7 Liquid crystal molecules follow an applied electric field. (Morris, 1993)

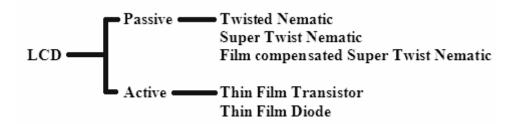

# 2.3.4 Liquid Crystal Display Types

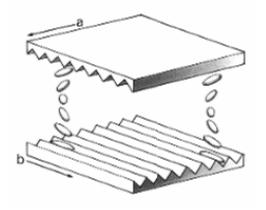

LCDs are broken up into two main groups: passive displays and active displays. Passive and active refer to the circuits that are responsible for activating pixels.

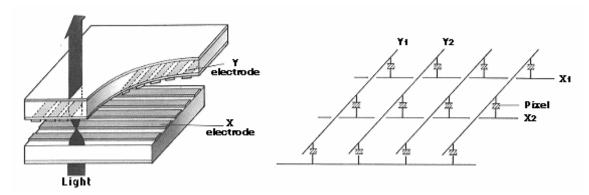

Passive LCDs use electrical components that do not supply their own energy to turn 'on' or 'off' desired pixels. A passive matrix LCD is made up of a set of multiplexed (a method of reducing the number of I/O lines needed) transparent electrodes. The electrodes are made of a conductive film, usually indium-tin oxide or ITO and are placed above and below the liquid crystal layer in a row/column formation (see Figure 2.8). The rows and columns are then connected to integrated circuits, which control when and where charge is delivered. To address a pixel the

column containing the pixel is sent a charge; the corresponding row is connected to ground. When sufficient voltage is placed across the pixel, the liquid crystal molecules align parallel to the electric field.

Figure 2.8 Structural and circuit level diagrams of a passive matrix. (Gurski & Quach, 2005)

Multiplexed passive screens were the solution to creating larger LCDs. In a ten by ten array of pixels one hundred separate connections would be needed to be able to address all of them. If the lines were multiplexed then only 20 connections would be needed (one for each row and column). In general the number of connections needed for non-multiplexed lines is M x N where 'M' and 'N' are the number of rows and columns in an array. When multiplexing is used, the number of connections is M+N. To activate pixels in a multiplexed array carefully timed voltage pulses are sent to corresponding rows and columns. Pulses are coordinated so that they reach the right pixel at the right time without activating unwanted pixels. Timing, duration and amplitude of pulses are controlled by driver circuitry external to the passive matrix. The diagram of LCD with color filter is shown at Figure 2.9.

Figure 2.9 Diagram of LCD with color filters added. (Gurski & Quach, 2005)

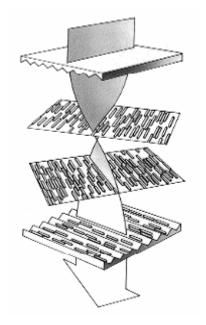

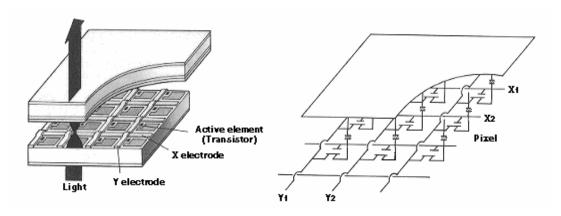

Active liquid crystal displays have a similar construction to the passive implementation. Just like a passive display, active LCDs use a semi transparent conductive grid to supply charge to the liquid crystal layer. The important difference is that the active displays have a transistor built into each pixel. This thin film transistor (TFT) acts like a switch precisely controlling the voltage each pixel receives. As shown in the diagram below the basic structure of an active matrix LCD or a TFT display is a common electrode placed above the liquid crystal matrix. Below the liquid crystal is a conductive grid connected to each pixel through a TFT. Inside each pixel the structure is as follows, the gate of each TFT is connected to the row electrode, the drain to the column electrode, and the source to the liquid crystal. To activate the display voltage is applied to each row electrode line by line. To turn on a pixel the gate lines have to be activated; this closes the switch and allows charge from the drain to flow to the source setting up an electric field between the source and the common electrode above. The column electrodes connected to the drain carry the data voltages (which pixels to activate and to what shade) and are synchronized to the gate pulses. Connected to the source of each TFT in parallel with the liquid crystal is a small capacitor. When a pulse is sent to the gate, charge flows from the drain to the source where the capacitor charges to the desired level. The purpose of the capacitor is to keep voltage applied to the liquid crystal molecules until the next

refresh cycle. Capacitors are sized large enough to keep a constant voltage on activate pixels, over the entire refresh cycle. Structure diagram and circuit diagram is shown at Figure 2.10.

Figure 2.10 Structural and circuit level diagrams of an active matrix. (Gurski & Quach, 2005)

LCD technology had been in development for almost forty years, and will continue into the near future. Each day new ways are devised to improve the brightness, contrast, and overall picture quality of LCDs. New materials are under research in order to give TFT screens faster refresh times, and to lower power usage. LCDs are making progress, but must continue to improve if they are to remain competitive against other emerging display technology.

# 2.4 Organic Light Emitting Diodes (OLEDs)

One of the next trends in display technology is Organic Light Emitting Diodes (OLEDs). Polymer Light Emitting Diodes (PLEDs), Small Molecule Light Emitting Diodes (SMOLEDS) and dendrimer technology are all variations of OLEDs. With all variations being made by electroluminescent substances (substances that emit light when excited by an electric current), OLED displays are brighter, offer more contrast, consume less power, and offer large viewing angles – all areas where LCDs fall short.

# 2.4.1 Fundamentals of OLEDs

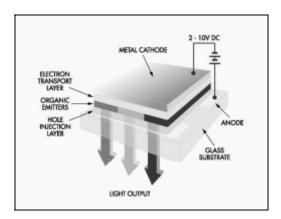

OLEDs are composed of light-emitting organic material sandwiched between two conducting plates, one of n-type material and one of p-type material. The molecular structure in n-type material, although electrically neutral, has an extra electron that is relatively free to move around the material. In p-type material the opposite is true. The lack of an electron creates a hole that is free to move about. The creation of the extra electron or the hole comes about because of the mismatch of valence electrons in the molecular structure of the p or n-type material. Applying a voltage between the two plates causes holes to be injected from the p-type substrate and electrons to be injected from the n-type substrate. When an Electron fills in a hole, it drops from a higher energy level to a lower one; consequently, this difference in energy is released as a photon of light (light particle). The wavelength of the light generated is dependant on the energy gaps of the emitting material. In order to produce visible light, these energy gaps have to be within 1.5 to 3.5 electron volts (eV). For example, a photon of 3.1 eV has a wavelength of 400 nm which is visible as a violet light. Therefore, the colors emitted are dependant on the molecular composition of the organic emissive material chosen for the OLED.

# 2.4.2 Structure and Types of OLEDs

OLEDs were first developed by Eastman Kodak in 1987. Their method of producing OLEDs was known as the Small Molecular method. Based on the Small Molecular method, PLEDs and dendrimers were later developed. While their structures remained approximately the same, the organic material was different.

Figure 2.17 OLED structure. (Antoniadis, 2004)

The structure of a basic SMOLED contains multiple layers of organic material. (See Figure 2.14) Depending on the organic chemicals that are used to generate the display, different manufacturing techniques can be used. The p-type layer, known as the anode, is made from a high work function material such as indium tin oxide (ITO) – known for its conductive and transparent properties. The next layer is an organic material which aids in the transportation of holes known as normal-propylbromide (NPB). Following this layer is one which aids in the transport of electrons; tris-8-ydroxyquinoline aluminum (alq3) is generally used to form it. Lastly, the ntype layer, known as the cathode, is made from a low work-function material such as MgAg (magnesium silver) to produce the electrons. In order to improve efficiency, a luminescent layer is normally added in between the two layers of organic material, and is generally composed of a mixture of alg3 and C540 (a carbon derivative). C540 is responsible for the added fluorescence. SMOLEDs require a complicated process of vacuum vapor deposition, where the deposition method involves sublimating the material in a vacuum. This process allows for a more accurate and better controlled application of these layers onto the display substrate; however, vapor vacuum deposition is also very complex, and as a result, this renders to higher manufacturing costs. Therefore, SMOLEDs are more suited for smaller displays such as cell phones, camera displays, etc. where they can produce excellent color displays with a long lifetime.

# 2.4.4 OLED Benefits

Because of the OLEDs' thin structure and excellent display qualities, it is ideal for use in flat-panel displays. OLEDs have many advantages compared to LCD technology – today's leader in this area. OLEDs are emissive displays (meaning they generate their own light), and as a result require no backlighting. Another significant advantage is OLED displays have extremely high switching speeds and as a result can handle high refresh rates required for full-motion video. OLEDs also have a large viewing angle as a result of its self-luminous effect.

# 2.5 Digital Light Processing (DLP)

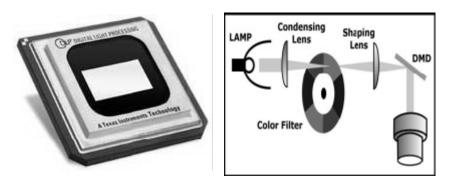

DLP technology is a system that uses an optical semiconductor developed by Dr. Larry Hornbeck of Texas Instruments in 1987. This device, known as a Digital Micromirror Device (DMD chip), is essentially a very precise light switch that can digitally modulate light through the use of 2 million hinge-mounted microscopic mirrors arranged in a rectangular array; each of these micromirrors are less than 10 microns (approximately one-fifth the width of a human hair). Combined with a digital video or graphic signal, a light source, and a projection lens, the mirrors of the DMD chip can reflect an all-digital image onto any surface. A DLP Chip and color display process is shown at Figure 2.15.

Figure 2.15 DMD chip and DLP color display process (Antoniadis, 2004

# 2.5.1 DLP Structure

By mounting these micromirrors on tiny hinges, they are able to tilt either toward the light source where they are noted as being "on" or away from the light source where they are noted as being "off". Consequently, depending on the state of these mirrors, a light or a dark pixel is projected onto the screen. The mirrors are instructed to switch on or off several thousand times per second by a digital signal entering the semiconductor. A lighter shade of grey is produced when a mirror is switched on more frequently than off; whereby a darker shade of grey is produced when a mirror is switched off more frequently than on. Using this method, DMD chips can generate up to 1024 shades of grey and consequently produce a highly detailed greyscale image.

# 2.5.2 DLP in Color

In most DLP systems, a color wheel is placed between the light source and the mirrored panel. As the color wheel spins, it causes the white light generated by the light source to filter into red, green, and blue light to fall on the DMD mirrors. When the on/off states of each mirror are coordinated with the flashes of colored light, the DLP system can generate approximately 16 million colors. For example, a purple pixel is created by switching on the mirror only when red or blue light is falling on it. Our eyes then combine these primary colors to see the intended purple.

### 2.5.3 DLP Uses

Projectors, TVs, and home theatre systems are currently based on DLP systems that use a single DMD chip. Larger venues like cinemas tend to use DLP systems that use three DMD chips. The difference being the white light generated by the light source is passed first through a prism and is then filtered into red, green, and blue.

Each DMD chip is then dedicated to each primary color and the reflected light is then combined and passed through the projector lens to a screen. The result is a system that can produce up to 35 trillion colors for the ultimate movie experience.

As mentioned previously, DLPs are currently limited to projection technology and have not been developed for smaller screen displays such as monitors and cell phones.

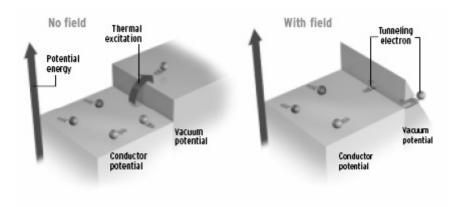

# 2.6 Field Emission Displays (FEDs)

Field emission displays (FEDs) function much like CRT technology. Instead of using one electron gun to emit electrons at the screen, FEDs use millions of smaller ones. The result is a display that can be as thin as an LCD, reproduce CRT-quality images, and be as large as a plasma display. Initial attempts in making emissive, flat-panel displays using metal tipped cathodes occurred nearly 20 years ago, however, with reliability, longevity, and manufacturing issues, these types of FEDs do not seem commercially viable.

# 2.6.1 Field Emission Fundamentals

The foundation of Field Emission technology is the extraction of electrons from a material using the "tunneling" effect. Tunneling describes the phenomenon of electrons being able to behave likes waves as well as like particles. Within a conductor, free electrons are generally mobile within a certain degree. What prevents these electrons from simply escaping the bounds of conductors is a potential energy barrier. In order to surpass this potential energy barrier, electrons must be provided with enough energy. However, with the tunneling effect, (see Figure 2.16) if a high enough electric field is applied outside the conductor, the strength of the potential energy barrier will be reduced, and consequently it will get to the point where an electron wave can extend itself across the barrier.

Figure 2.16 The tunneling effect (Guarski & Quach, 2005)

The emitted current, or moving electrons, depends on the electric field strength, the emitting surface, and the work function. In order for field emission to function, the electric field has to be extremely high: up to 3 x 107 V/cm. This value, though large, is accessible by the fact that field amplification increases with a decreasing curvature radius indicating that the pointier the object, the more charge it will have at its tip, and hence the larger the electric field. As a result, if such a material can be found, a moderate voltage will cause the tunneling effect, and hence allow electrons to escape into free space without the heating of the cathode like the traditional Cathode Ray Tube (CRT) technology.

## 2.6.2 Traditional FED Structure

The basic structure of the first FED was comprised of millions of vacuum tubes, called microtips. Each tube was red, green, or blue and together, formed one pixel. These microtips were sharp cathode points made from molybdenum from which electrons, under a voltage difference, would be emitted towards a positively charged anode where red, blue, and green phosphors were struck, and as a result emit light through the glass display. Unlike CRTs, color was displayed sequentially, meaning the display processed all the green information first, then refreshed the screen with red information, and finally blue.

The advantages of the traditional FED included the fact that they only produced light when the pixels were "on", and as a result power consumption was dependent on the display content. A FED also generated light from the front of the pixel, providing an excellent viewing angle of 160 degrees both vertically and horizontally. These FEDs also had a high product yield as thousands of electron emitters were in place for each pixel; they suffered no brightness loss even if 20% of the emitters failed. Though this technology seemingly could have been a huge contender in the flat panel business, it was plagued with many problems due to the extreme electrical environment of the display. One problem being the metal molybdenum, used to make the microtips, would become so heated that local melting would result and consequently deform its sharp tips needed to form the electric field used for electron emission. Another problem caused by the electrical environment was the hot cathodes would react with the residual gases in the vacuum consequently reducing the field emission even more.

# 2.7 Backlight Technologies

A key component in the deployment of Liquid Crystal Display (LCD) technology for outdoor applications is the integration of a high bright backlight (or light source) behind the LCD glass. There are several different LCD backlight technologies being employed in the outdoor digital signage market today; Cold Cathode Fluorescent Lamp (CCFL), External Electrode Fluorescent Lamp (EEFL), Hot Cathode Fluorescent Lamp (HCFL), Light Emitting Diode (LED), and Flat Fluorescent Lamp (FFL). There are advantages and disadvantages for each technology as it pertains to outdoor environments where displays are typically subject to direct sunlight across a wide range of temperature and humidity conditions. In order to perform well in these environments, the backlight must meet certain minimum criteria for outdoor use that include brightness, reliability, efficiency, thermal packaging, and color reproduction. In LCD panels, the majority of power consumption in the product comes from the backlight source. With today's energy costs skyrocketing, the efficiency and longevity of the backlight plays a critical role in the cost of operation, and ultimately in the total cost of ownership. This white paper provides a comparison of the current backlight technologies available today for outdoor display applications and provides insight into Delphi's long term backlight technology development roadmap.

# 2.7.1 Cold Cathode Fluorescent Lamp (CCFL)

Cold Cathode Fluorescent Lamps (CCFL), (other abbreviations include CFL (Cold Florescent Lamp) and CCFT (Cold Cathode Fluorescent Tube)) are the most commonly used form of LCD backlighting at present. This is due to exceptional brightness and full spectral output. A CCFL is a thin (outer diameters as small as 1.6mm) glass tube with an internal vacuum. A pressurized Neon/Argon mix sealed within the fluorescent tube is excited by a high AC voltage with a striking voltage > 1000 V and a sustained voltage of 100 ~ 300 VAC (please check individual data sheets as appropriate). A DC/AC inverter is required to generate these high alternating voltages. The electrons within the gas become highly energized and when they strike the fluorescent material coated on the inner surface of the tube cause the fluorescent material to fluoresce and emit white light. The CCFL is normally used with a light-guide to illuminate a surface area (Figure 2.17).

Figure 2.16 Cold Cathode Fluorescent Lamp (CCFL) with Light-Guide (Chaddertor, 1996)

One potential issue with Cold Cathode Fluorescent Lamps (CCFLs) is operation in cold temperatures. When a CCFL gets very cold (below 0°C), the strike voltages become excessive and it may not turn on at all. In addition, the lifetime of the CCFL at low temperatures will be reduced. At normal operating temperatures, CCFLs have a very long life – 50,000 hours is common for new generation lamps.

The CCFL is used with two main configurations. The primary configuration used in LCD backlighting is line source with a light-guide (sometimes called side lighting). The other configuration which increases the brightness at the expense of the power requirements uses several CCFLs directly behind the LCD without the use of a light-guide.

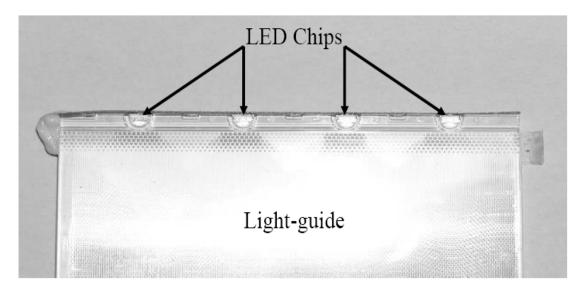

# 2.7.1 Light Emitting Diodes (LED)

Light Emitting Diode (LED) backlighting is a popular backlighting method for small and medium LCDs. The advantages of LED backlighting are low cost (at least for small area displays), long life, immunity to vibration, low operational voltage, and precise control over its intensity. LED backlights come in a variety of colors, with white becoming a cost effective and very popular option. LED backlights offer

a long operating life of 15,000 hours minimum for white and can be much longer for other colors. Being a solid state device, they are configured to operate typically with +5VDC power, so no inverter is required. The LED backlighting is also used in conjunction with a light-guide (Figure 2.17).

Figure 2.17 Light Emitting Diode (LED) with Light-Guide (Chaddertor, 1996)

LED backlights have two basic configurations. In the Array lit configuration there are many LEDs mounted uniformly behind the display offering a very bright illumination but with high power consumption (*Figure 5*). In the Edge lit configuration, the LEDs are mounted on the edge of a plastic light guide (*Figure 2*) and the light is focused into the light-guide (*Figure 6*). The edge lit configuration offers a thinner package with lower power consumption and is the most widely used system in the industry. (Yu, 2006)

## 2.7.2.1 Advantages of LEDs

The main advantages of LEDs are:

- Long Service Life

- 100,000 hours time to ½ life- YG, Red and Amber

- 50,000 hours Green

- 20,000 to 40,000 hours for Blue and White

- Good environmental performance including high UV, high temperature and high humidity resistance

- High MBTF

- Solid-state chip embedded in epoxy- nothing to break or burn out

- LED consumption is increasing, driving costs down

- Low heat generation

- No EMI or RFI

- Low Power (5 to 30 mA at 3.6 or 2.2 Vdc)

- New narrower beam, light focusing packages that are better utilized in light guides

- Many color choices

# 2.7.2.2 Disadvantage of LEDs

The main disadvantages of LEDs are:

- Sensitive to ESD

- Sensitive to voltage spikes

- Heat dissipation in some applications

- Not true full spectrum White LED (unless tri-color) (Lim, 2006)

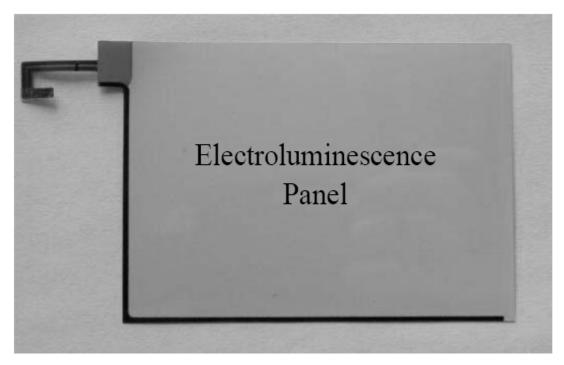

## 2.7.3 Electroluminescent Panel (ELP)

Electro Luminescent (EL) backlights use a solid state phenomenon based on colored phosphors to generate light when an AC voltage is applied to the EL panel. EL backlights are very thin, lightweight and provide an even distribution of light, without the need of a light-guide (Figure 2.18).

Figure 2.18 Electroluminescent Panel (ELP) (Lim, 2006)

They are available in a variety of colors, with white being the most popular for use with LCDs. While their power consumption is fairly low, they require voltages of 100 VAC @ 400Hz. This is supplied by an inverter that converts a 5, 12 or 24 VDC input to the AC output. EL backlights also have a limited life of 3,000 to 5,000 hours to half brightness (half-life). The limited brightness and lifetime of EL panels has made them unpopular and they are rarely used to backlight graphical LCDs. EL has only one configuration, broad area emitter. (Lim, 2006)

Backlight technology will play a critical role in the development of the LCD market going forward. As more importance is placed on picture quality, lifetime, and power consumption, the technologies that provide benefits in these areas will win out in the long run. Today, the vast majority of LCD-TVs utilize CCFL backlights. Accordingly, CCFL will continue to play an important role in the foreseeable future due to its good efficiency and price-to-performance ratio. The two emerging backlight technologies that are being embraced by the industry are EEFL and LED. EEFL offers improved power efficiency, though much work remains to solve the mercury issue. LED backlights have the most promising market and environmental the mid-term improvement potential in long-term future. to

#### CHAPTER THREE

#### FIELD PROGRAMMABLE GATE ARRAY

#### 3.1 Introduction

Prompted by the development of new types of sophisticated field-programmable devices (FPDs), the process of designing digital hardware has changed dramatically over the past few years. Unlike previous generations of technology, in which boardlevel designs included large number of SSI chips containing basic gates, virtually every digital design produced today consists mostly of high-density devices. This applies not only to custom devices like processors and memory, but also for logic circuits such as state machine controllers, counters, registers, and decoders. When such circuits are destined for high-volume systems they have been integrated into high-density gate arrays. However, gate array NRE costs often are too expensive and gate arrays take too long to manufacture to be viable for prototyping or other lowvolume scenarios. For these reasons, most prototypes, and also many production designs are now built using FPDs. The most compelling advantages of FPDs are instant manufacturing turnaround, low start-up costs, low financial risk and (since programming is done by the end user) ease of design changes. The market for FPDs has grown dramatically over the past decade to the point where there is now a wide assortment of devices to choose from. A designer today faces a daunting task to research the different types of chips, understand what they can best be used for, choose a particular manufacturer's product, learn the intricacies of vendor-specific software and then design the hardware. Confusion for designers is exacerbated by not only the sheer number of FPDs available, but also by the complexity of the more sophisticated devices. The emphasis is on devices with relatively high logic capacity; all of the most important commercial products are discussed. Before proceeding, we provide definitions of the terminology in this field. This is necessary because the technical become somewhat inconsistent jargon has over the past few years as companies have attempted to compare and contrast their products in literature.

A field-programmable gate array (FPGA) is a semiconductor device that can be configured by the customer or designer after manufacturing—hence the name "field-programmable". FPGAs are programmed using a logic circuit diagram or a source code in a hardware description language (HDL) to specify how the chip will work. They can be used to implement any logical function that an application-specific integrated circuit (ASIC) could perform, but the ability to update the functionality after shipping offers advantages for many applications. (BETZ, 2000)

FPGAs contain programmable logic components called "logic blocks", and a hierarchy of reconfigurable interconnects that allow the blocks to be "wired together"—somewhat like a one-chip programmable breadboard. Logic blocks can be configured to perform complex combinational functions, or merely simple logic gates like AND and XOR. In most FPGAs, the logic blocks also include memory elements, which may be simple flip-flops or more complete blocks of memory.

The FPGA industry sprouted from programmable read only memory (PROM) and programmable logic devices (PLDs). PROMs and PLDs both had the option of being programmed in batches in a factory or in the field (field programmable), however programmable logic was hard-wired between logic gates.

#### 3.2 Modern Developments

A recent trend has been to take the coarse-grained architectural approach a step further by combining the logic blocks and interconnects of traditional FPGAs with embedded microprocessors and related peripherals to form a complete "system on a programmable chip". This work mirrors the architecture by Ron Perlof and Hana Potash of Burroughs Advanced Systems Group which combined a reconfigurable CPU architecture on a single chip called the SB24. That work was done in 1982. Examples of such hybrid technologies can be found in the Xilinx Virtex-II PRO and Virtex-4 devices, which include one or more PowerPC processors embedded within

34

the FPGA's logic fabric. The Atmel FPSLIC is another such device, which uses an

AVR processor in combination with Atmel's programmable logic architecture.

An alternate approach to using hard-macro processors is to make use of "soft"

processor cores that are implemented within the FPGA logic. As previously

mentioned, many modern FPGAs have the ability to be reprogrammed at "run time,"

and this is leading to the idea of reconfigurable computing or reconfigurable systems

— CPUs that reconfigure themselves to suit the task at hand. The Mitrion Virtual

Processor from Mitrionics is an example of a reconfigurable soft processor,

implemented on FPGAs. However, it does not support dynamic reconfiguration at

runtime, but instead adapts itself to a specific program.

Additionally, new, non-FPGA architectures are beginning to emerge. Software-

configurable microprocessors such as the Stretch S5000 adopt a hybrid approach by

providing an array of processor cores and FPGA-like programmable cores on the

same chip.

3.2.1 Gates

1987: 9,000 gates, Xilinx

1992: 600,000, Naval Surface Warfare Department

Early 2000s: Millions

3.2.2 Market Size

1985: First commercial FPGA technology invented by Xilinx

1987: \$14 million

~1993: >\$385 million

2005: \$1.9 billion

2010 estimates: \$2.75 billion

## 3.2.3 FPGA Design

- 10,000

- 2005: 80,000

- 2008:90,000

- 2010 estimates: 110,000 (Hewlett-Packard Co., 2001)

# 3.3 FPGA Comparisons

Historically, FPGAs have been slower, less energy efficient and generally achieved less functionality than their fixed ASIC counterparts. A combination of volume, fabrication improvements, research and development, and the I/O capabilities of new supercomputers have largely closed the performance gap between ASICs and FPGAs.

Advantages include a shorter time to market, ability to re-program in the field to fix bugs, and lower non-recurring engineering costs. Vendors can also take a middle road by developing their hardware on ordinary FPGAs, but manufacture their final version so it can no longer be modified after the design has been committed.

Xilinx claims that several market and technology dynamics are changing the ASIC/FPGA paradigm:

- IC costs are rising aggressively

- ASIC complexity has bolstered development time and costs

- R&D resources and headcount is decreasing

- Revenue losses for slow time-to-market are increasing

- Financial constraints in a poor economy are driving low-cost technologies

These trends make FPGAs a better alternative than ASICs for a growing number of higher-volume applications than they have been historically used for, to which the company attributes the growing number of FPGA design starts.

The primary differences between CPLDs and FPGAs are architectural. A CPLD has a somewhat restrictive structure consisting of one or more programmable sum-

of-products logic arrays feeding a relatively small number of clocked registers. The result of this is less flexibility, with the advantage of more predictable timing delays and a higher logic-to-interconnect ratio. The FPGA architectures, on the other hand, are dominated by interconnect. This makes them far more flexible (in terms of the range of designs that are practical for implementation within them) but also far more complex to design for.

Another notable difference between CPLDs and FPGAs are the presence in most FPGAs of higher-level embedded functions (such as adders and multipliers) and embedded memories, as well as to have logic blocks implement decoders or mathematical functions.

Some FPGAs have the capability of partial re-configuration that lets one portion of the device be re-programmed while other portions continue running.

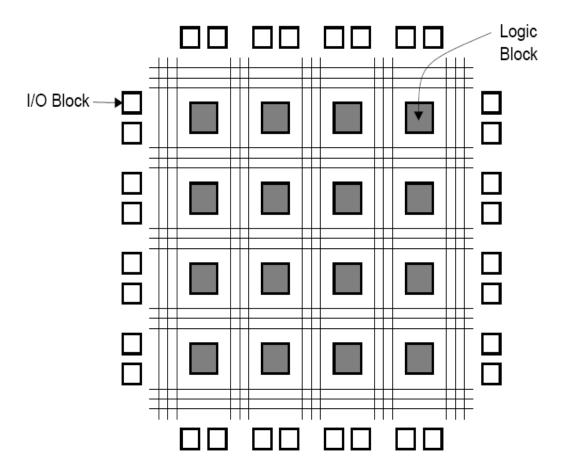

#### 3.4 FPGA Architecture

The most common FPGA architecture consists of an array of configurable logic blocks (CLBs), I/O pads, and routing channels. Generally, all the routing channels have the same width (number of wires). Multiple I/O pads may fit into the height of one row or the width of one column in the array.

An application circuit must be mapped into an FPGA with adequate resources. While the number of CLBs and I/Os required is easily determined from the design, the number of routing tracks needed may vary considerably even among designs with the same amount of logic. (For example, a crossbar switch requires much more routing than a systolic array with the same gate count.) Since unused routing tracks increase the cost (and decrease the performance) of the part without providing any benefit, FPGA manufacturers try to provide just enough tracks so that most designs that will fit in terms of LUTs and IOs can be routed. This is determined by estimates such as those derived from Rent's rule or by experiments with existing designs.

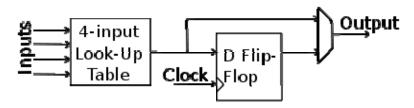

A classic FPGA logic block consists of a 4-input lookup table (LUT), and a flipflop, as shown at Figure 3.1. In recent years, manufacturers have started moving to 6input LUTs in their high performance parts, claiming increased performance.

Figure 3.1 Typical logic block (BETZ, 2000)

There is only one output, which can be either the registered or the unregistered LUT output. The logic block has four inputs for the LUT and a clock input. Since clock signals (and often other high-fanout signals) are normally routed via special-purpose dedicated routing networks in commercial FPGAs, they and other signals are separately managed.

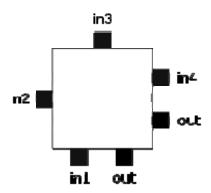

For this example architecture, the locations of the FPGA logic block pins are shown below at Figure 3.2.

Figure 3.2 Logic Block Pin Locations (BETZ, 2000)

Each input is accessible from one side of the logic block, while the output pin can connect to routing wires in both the channel to the right and the channel below the logic block.

Each logic block output pin can connect to any of the wiring segments in the channels adjacent to it.

Similarly, an I/O pad can connect to any one of the wiring segments in the channel adjacent to it. For example, an I/O pad at the top of the chip can connect to

any of the W wires (where W is the channel width) in the horizontal channel immediately below it.

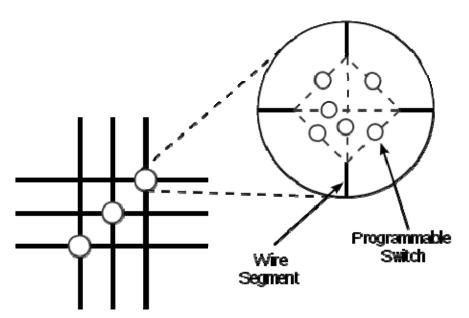

Generally, the FPGA routing is unsegmented. That is, each wiring segment span only one logic block before it terminates in a switch box. By turning on some of the programmable switches within a switch box, longer paths can be constructed. For higher speed interconnect, some FPGA architectures use longer routing lines that span multiple logic blocks.

Whenever a vertical and a horizontal channel intersect, there is a switch box. In this architecture, when a wire enters a switch box, there are three programmable switches that allow it to connect to three other wires in adjacent channel segments. The pattern, or topology, of switches used in this architecture is the planar or domain-based switch box topology and can be seen in Figure 3.3. In this switch box topology, a wire in track number one connects only to wires in track number one in adjacent channel segments, wires in track number 2 connect only to other wires in track number 2 and so on. The figure below illustrates the connections in a switch box.

Figure 3.3 Switch box topology (BETZ, 2000)

Modern FPGA families expand upon the above capabilities to include higher level functionality fixed into the silicon. Having these common functions embedded into the silicon reduces the area required and gives those functions increased speed compared to building them from primitives. Examples of these include multipliers, generic DSP blocks, embedded processors, high speed IO logic and embedded memories.

FPGAs are also widely used for systems validation including pre-silicon validation, post-silicon validation, and firmware development. This allows chip companies to validate their design before the chip is produced in the factory, reducing the time to market.

Figure 4.4 Structure of FPGA (BETZ, 2000)

# 4.4 FPGA Design and Programming

To define the behavior of the FPGA, the user provides a hardware description language (HDL) or a schematic design. The HDL form might be easier to work with when handling large structures because it's possible to just specify them numerically rather than having to draw every piece by hand. On the other hand, schematic entry can allow for easier visualization of a design.

Then, using an electronic design automation tool, a technology-mapped netlist is generated. The netlist can then be fitted to the actual FPGA architecture using a process called place-and-route, usually performed by the FPGA company's proprietary place-and-route software. The user will validate the map, place and route results via timing analysis, simulation, and other verification methodologies. Once the design and validation process is complete, the binary file generated (also using the FPGA company's proprietary software) is used to (re)configure the FPGA.

The source files are fed to a software suite from the FPGA/CPLD vendor that through different steps will produce a file. This file is then transferred to the FPGA/CPLD via a serial interface (JTAG) or to an external memory device like an EEPROM.

The most common HDLs are VHDL and Verilog, although in an attempt to reduce the complexity of designing in HDLs, which have been compared to the equivalent of assembly languages, there are moves to raise the abstraction level through the introduction of alternative languages.

To simplify the design of complex systems in FPGAs, there exist libraries of predefined complex functions and circuits that have been tested and optimized to speed up the design process. These predefined circuits are commonly called *IP cores*, and are available from FPGA vendors and third-party IP suppliers (rarely free, and typically released under proprietary licenses). Other predefined circuits are available from developer communities such as OpenCores (typically *free*, and released under the GPL, BSD or similar license), and other sources. (Hewlett-Packard Co., 2001)

In a typical design flow, an FPGA application developer will simulate the design at multiple stages throughout the design process. Initially the RTL description in VHDL or Verilog is simulated by creating test benches to simulate the system and observe results. Then, after the synthesis engine has mapped the design to a netlist, the netlist is translated to a gate level description where simulation is repeated to confirm the synthesis proceeded without errors. Finally the design is laid out in the FPGA at which point propagation delays can be added and the simulation run again with these values back-annotated onto the netlist.

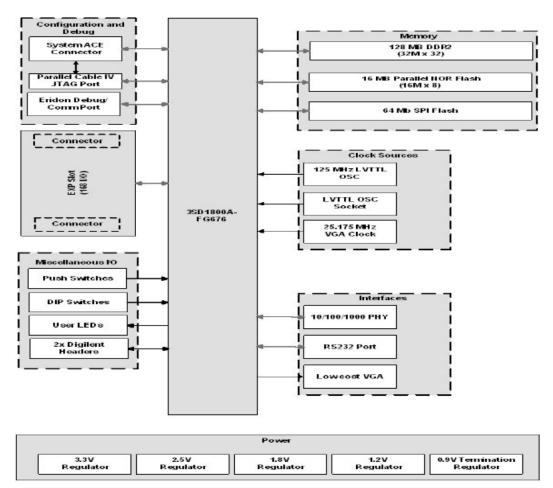

## 4.5 Which FPGA is Chosen For This Project

For image processing applications, generally DSP FPGA chips are used. They have a lot of differential I/O pins and much more gates than other FPGA chipsets. This project is similar to image processing application so a DSP FPGA is chosen. Spartan 3A DSP1800A video starter kit is used. See Appendix K for datasheet.

#### **CHAPTER FOUR**

## LOCAL DIMMING APPLICATION

# 4.1 Technical Information

## 4.1.1 LED Backlight Unit and Its Types

#### 4.1.1.1 LED Overview

LEDs are the fastest growing backlight technology on the market today. They provide many benefits as a backlight source for LCDs including reasonably good efficiency, a wider range of color reproduction, enhanced contrast ratio (due to the option of arbitrarily scaling/dimming individual display areas), low voltage operation, mercury-free construction, good thermal dissipation properties and high luminance.

Many manufacturers have designed very large LCD-TV products utilizing red, green and blue (RGB) LEDs for the backlight and have achieved good performance. However, RGB LED backlights demand color mixing technology in order to overcome unevenness of luminance. Color mixing has significantly improved with an increased understanding of the design and function of direct backlight concept. Today, RGB LED clusters (usually 1x red, 2x green, and 1x blue) are grouped in matrices with some space provided between clusters to facilitate good color mixing and to minimize the need for design of thermal radiation structures. Another critical factor to consider in LED backlight design is the need for control of system temperature, as this is essential in order to avoid color shift, which is another challenge in LED backlight systems. Many new backlights are being designed utilizing white LED technology.

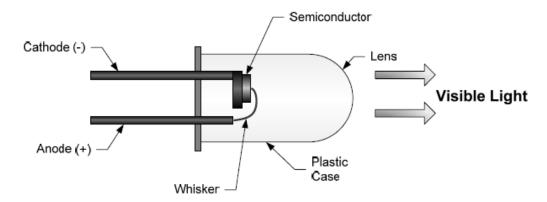

An LED is a semiconductor device that creates light using solid-state electronics. A diode is composed of a layer of electron rich material separated by a layer of electron deficient material which forms a junction. Power applied to this junction excites the electrons in the electron rich material leading to photon emission and the

creation of light. Depending on the chemical composition of the semiconductor layers, the color of light emission will vary.

Figure 4.1 LED Construction

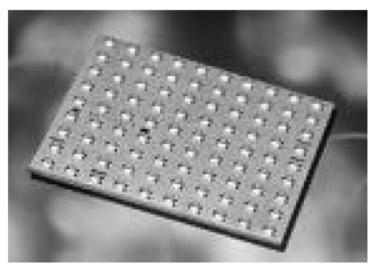

For outdoor applications, high bright backlights are constructed as a matrix of LEDs covered by a set of filters to diffuse and balance the light across the entire surface of the LCD. A typical LED backlight matrix is shown in the Figure 4.2.

Figure 4.2 Typical LED matrix backlight

#### 4.1.2 Contrast Ratio

The contrast ratio is a measure of a display system, defined as the ratio of the luminance of the brightest color (white) to that of the darkest color (black) that the system is capable of producing. A high contrast ratio is a desired aspect of any display, but with the various methods of measurement for a system or its part, remarkably different measured values can sometimes produce similar results.

Contrast ratio ratings provided by different manufacturers of display devices are not necessarily comparable to each other due to differences in method of measurement, operation, and unstated variables. Manufacturers have traditionally favored measurement methods that isolate the device from the system, whereas other designers have more often taken the effect of the room into account. An ideal room would absorb all the light reflecting from a projection screen or emitted by a CRT, and the only light seen in the room would come from the display device. With such a room, the contrast ratio of the image would be the same as the device. Real rooms reflect some of the light back to the displayed image, lowering the contrast ratio seen in the image.

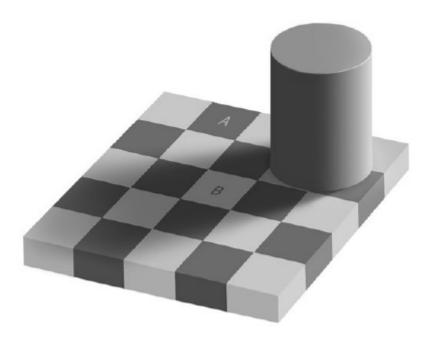

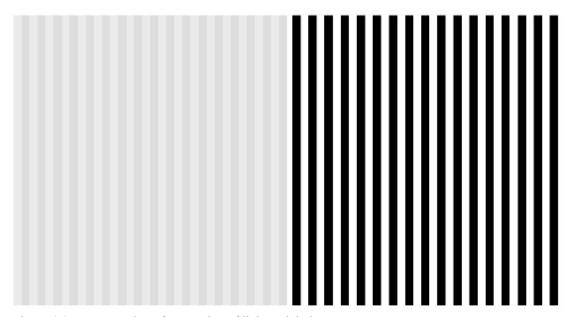

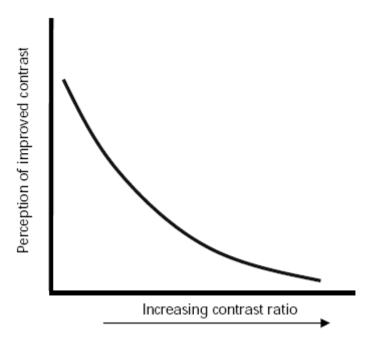

Moving from a system that displays a static motionless image to a system that displays a dynamic, changing picture slightly complicates the definition of the contrast ratio, because of the need to take into account the extra temporal dimension to the measuring process. Thus the ratio of the luminosity of the brightest and the darkest color the system is capable of producing simultaneously at any instant of time is called static contrast ratio, while the ratio of the luminosity of the brightest and the darkest color the system is capable of producing over time is called dynamic contrast ratio. Demonstration of brightness perception can be seen at Figure 4.3.

Figure 4.3 Demonstration of brightness perception

## 4.1.2.1 Methods of Contrast Ratio Measurements

Many display devices favor the use of the *full on/full off* method of measurement, as it cancels out the effect of the room and results in an ideal ratio. Equal proportions of light reflect from the display to the room and back in both "black" and "white" measurements, as long as the room stays the same. This will inflate the light levels of both measurements proportionally, leaving the black to white luminance ratio unaffected.

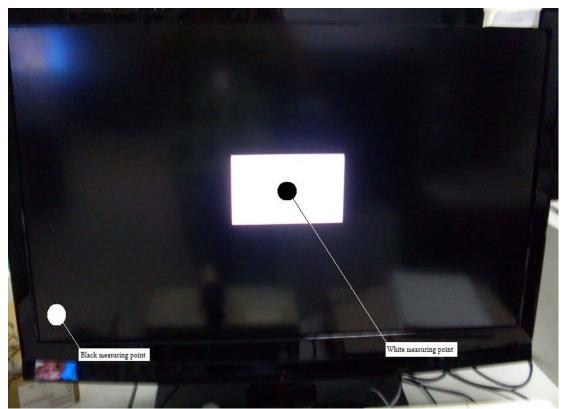

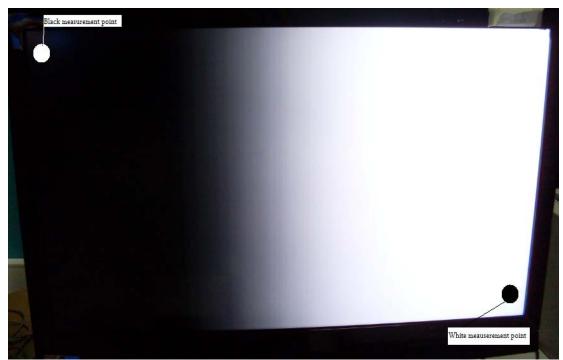

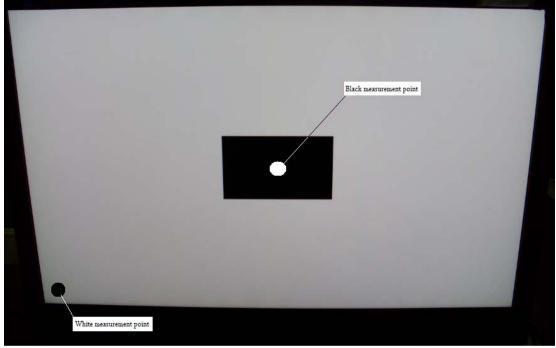

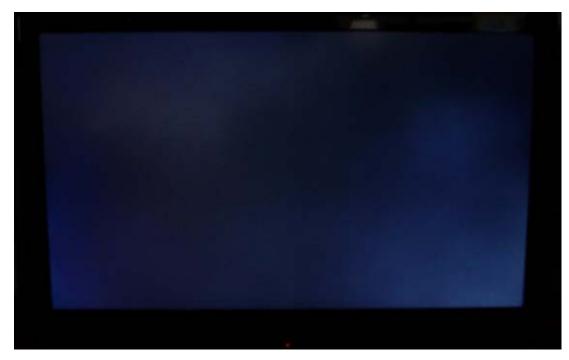

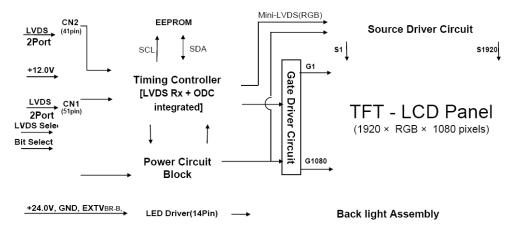

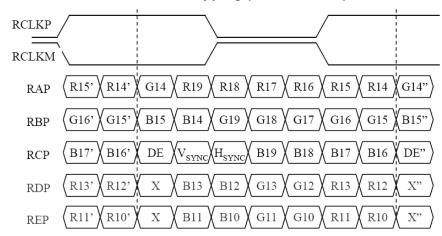

Some manufacturers have gone as far as using different device parameters for the three tests, even further inflating the calculated contrast ratio. With DLP projectors, one method to do this is to enable the clear sector of the color filter wheel for the "on" part and disable it for the "off" part. This practice is rather dubious, as it will be impossible to reproduce such contrast ratios with any useful image content.