## DOKUZ EYLÜL UNIVERSITY GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

# DESIGN AND IMPLEMENTATION OF AN INTERACTIVE FLAT PANEL DISPLAY

by Yunus YÜCEL

> July, 2015 İZMİR

## DESIGN AND IMPLEMENTATION OF AN INTERACTIVE FLAT PANEL DISPLAY

A thesis Submitted to the

Graduate School of Natural and Applied Sciences of Dokuz Eylül University in Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical and Electronics Engineering

> by Yunus YÜCEL

> > July, 2015 İZMİR

#### M.Sc THESIS EXAMINATION RESULT FORM

We have read the thesis entitled "DESIGN AND IMPLEMENTATION OF AN INTERACTIVE FLAT PANEL DISPLAY" completed by YUNUS YÜCEL under supervision of Asst. Prof. Dr. ÖZGÜR TAMER and we certify that in our opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Asst. Prof. Dr. Özgür TAMER Supervisor

Prof. Dr. Uğur ÇAM (Jury Member)

Prof. Dr. Mustala GÜNDÜZALP (Jury Member)

Prof.Dr. Ayşe OKUR Director Graduate School of Natural and Applied Sciences

#### ACKNOWLEDGEMENTS

I would like to thank Assc. Prof. Dr. Özgür TAMER for giving me the opportunity of implementing my thesis in this useful area of consumer electronics and sharing his excellent experience in electronics.

I would like to thank Prof. Dr. Uğur ÇAM for sharing his wide knowledge about electronic circuit design with me.

I would also like to thank Vestel Electronics and my colleagues at Vestel for sharing the test data and procedures about the system.

I also would like to thank to my wife for her never ending support throughout my life.

I dedicate this thesis to my daughter "VERA".

Yunus YÜCEL

## DESIGN AND IMPLEMENTATION OF AN INTERACTIVE FLAT PANEL DISPLAY

#### ABSTRACT

The thesis will describe full system design of an interactive flat panel display and approval phases in detail. Thesis will explain all the blocks of the interactive flat panel display such as power board, OPS (PC) board and monitor board in detail. Each design steps are explained in the thesis such as schematic design, PCB design (layout), system design and EMC and Safety approvals. EMC (Electromagnetic Compatibility) and Safety concepts and test procedures related with the interactive flat panel display will be mentioned before the mainboard EMC and Safety tests are mentioned. Thesis includes a brief explanation of flat panel display technology and Intel OPS standard as well.

**Keywords:** Mainboard design, interactive flat panel display, digital signage, OPS, electromagnetic compatibility

#### ETKİLEŞİMLİ EKRAN TASARIMI VE UYGULAMALARI

#### ÖZ

Tez, yüksek çözünürlüklü düz panel ekranlı etkileşimli ekranlar, bilgilendirme ekranları veya dijital reklam panoları tasarımını detaylı bir şekilde anlatmaktadır. Öncelikle sistem tasarım aşaması, sonrasında ise anakart tasarımının aşamaları (devre şeması çizimi, baskı devre tasarımı) ve anakart tasarım blokları detaylı bir şekilde anlatılmıştır. Anakart tasarımından sonra bu anakartın sistem entegrasyonu ve bu sistemin tüm test aşamalarından bahsedilmiştir. Tezde ayrıca, bir pazar standardı olan OPS (Open Pluggable Specification) standardından bahsedilmiştir. Avrupa standartlarına göre elektromanyetik uyumluluk testleri ve ürün güvenliği testleri yapılmış ve bu testlerden bahsedilmiştir. Tezde, düz panel teknolojisine de kısaca yer verilmiştir.

Anahtar kelimeler: Anakart tasarımı, etkileşimli ekranlar, dijital bilgilendirme ekranları, OPS, elektromanyetik uyumluluk

### CONTENTS

| M.Sc. THESIS EXAMINATION RESULT FORMi                     | i |

|-----------------------------------------------------------|---|

| ACKNOWLEDGEMENTSii                                        | i |

| ABSTRACTiv                                                | 1 |

| ÖZ                                                        | 1 |

| LIST OF FIGURES                                           | ζ |

| LIST OF TABLES                                            | i |

| CHAPTER ONE - INTRODUCTION 1                              | L |

| CHAPTER TWO – TFT-LCD PANEL DISPLAYS 4                    | ł |

| 2.1 A Brief Information about TFT-LCDs                    | 1 |

| 2.1.1 TFT LCD Structure                                   | 5 |

| 2.1.2 Working Principle of TFT LCDs                       | 5 |

| 2.1.3 Types of TFT LCDs                                   | 3 |

| 2.1.4 Driving Methods for TFT-LCDs                        | 3 |

| 2.1.5 TFT-LCD Panel Controlling and Driving Method        | ) |

| 2.1.6 Gray-scale and Color Generation                     | L |

| 2.2 Backlight Technology of TFT-LCD Panels 12             | 2 |

| 2.2.1 CCFL Backlight Technology12                         | 2 |

| 2.2.2 LED Backlight Technology 13                         | 3 |

| 2.2.3 Comparison of CCFL and LED Backlight Technologies14 | ł |

| CHAPTER THREE – SYSTEM DESIGN 15                          | 5 |

| 3.1 Monitor Board Design                                  | 5 |

| 3.1.1 Schematics Design                                   | 5 |

| 3.1.1.1 Scalar Block                                      | 7 |

| 3.1.1.1.1 Features of RTD2482D 19                         | ) |

| 3.1.1.2 Power Block                                                                                                                                                                                                                  |                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 3.1.1.2.1 TPS54229 Synchr                                                                                                                                                                                                            | conous Buck Converter                     |

| 3.1.1.2.2 LM1117 Low Dro                                                                                                                                                                                                             | opout Regulator                           |

| 3.1.1.3 Audio Block                                                                                                                                                                                                                  |                                           |

| 3.1.1.4 USB Switch                                                                                                                                                                                                                   |                                           |

| 3.1.2 Layout Design                                                                                                                                                                                                                  |                                           |

| 3.1.2.1 20H Rule at PCB Desi                                                                                                                                                                                                         | gn                                        |

| 3.2 OPS (Open Pluggable Specificat                                                                                                                                                                                                   | tion) Board and Interface 30              |

| 3.2.1 80 pin OPS Connector                                                                                                                                                                                                           |                                           |

| 3.2.1.1 Pin Assignment of 80                                                                                                                                                                                                         | pin Connector                             |

| 3.2.2 OPS Signals Description                                                                                                                                                                                                        |                                           |

| 3.2.2.1 UART Signals                                                                                                                                                                                                                 |                                           |

| 3.2.2.2 Control Signals                                                                                                                                                                                                              |                                           |

| 3.2.2.3 Reference Design Exam                                                                                                                                                                                                        | mples for Control Signals 41              |

| 3.3 SMPS Power Supply                                                                                                                                                                                                                |                                           |

| 3.4 I/R Touch Screen                                                                                                                                                                                                                 |                                           |

|                                                                                                                                                                                                                                      |                                           |

|                                                                                                                                                                                                                                      |                                           |

| CHAPTER FOUR – RESULTS                                                                                                                                                                                                               |                                           |

| CHAPTER FOUR – RESULTS                                                                                                                                                                                                               |                                           |

|                                                                                                                                                                                                                                      | <b></b>                                   |

| 4.1 Board Standalone Tests                                                                                                                                                                                                           |                                           |

| 4.1 Board Standalone Tests<br>4.1.1 Power Board Test                                                                                                                                                                                 |                                           |

| <ul><li>4.1 Board Standalone Tests</li><li>4.1.1 Power Board Test</li><li>4.1.2 Monitor Board Tests</li></ul>                                                                                                                        |                                           |

| <ul><li>4.1 Board Standalone Tests</li><li>4.1.1 Power Board Test</li><li>4.1.2 Monitor Board Tests</li></ul>                                                                                                                        |                                           |

| <ul> <li>4.1 Board Standalone Tests</li> <li>4.1.1 Power Board Test</li> <li>4.1.2 Monitor Board Tests</li> <li>4.1.3 Touch Screen Tests</li> </ul>                                                                                  |                                           |

| <ul> <li>4.1 Board Standalone Tests</li> <li>4.1.1 Power Board Test</li> <li>4.1.2 Monitor Board Tests</li> <li>4.1.3 Touch Screen Tests</li> </ul>                                                                                  |                                           |

| <ul> <li>4.1 Board Standalone Tests</li> <li>4.1.1 Power Board Test</li> <li>4.1.2 Monitor Board Tests</li> <li>4.1.3 Touch Screen Tests</li> <li>CHAPTER FIVE – DESIGN APPRO</li> </ul>                                             |                                           |

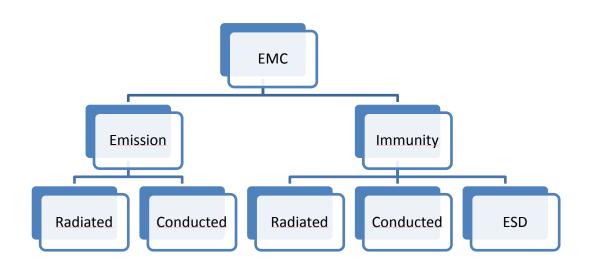

| <ul> <li>4.1 Board Standalone Tests</li> <li>4.1.1 Power Board Test</li> <li>4.1.2 Monitor Board Tests</li> <li>4.1.3 Touch Screen Tests</li> <li>CHAPTER FIVE – DESIGN APPRO</li> <li>5.1 EMC (Electromagnetic Compatie)</li> </ul> | 49<br>49<br>51<br>52<br>DVAL TESTS        |

| <ul> <li>4.1 Board Standalone Tests</li> <li>4.1.1 Power Board Test</li></ul>                                                                                                                                                        | 49<br>49<br>51<br>52<br><b>DVAL TESTS</b> |

| <ul> <li>4.1 Board Standalone Tests</li></ul>                                                                                                                                                                                        | 49<br>49<br>51<br>52<br><b>DVAL TESTS</b> |

| <ul> <li>4.1 Board Standalone Tests</li></ul>                                                                                                                                                                                        | 49<br>49<br>51<br>52<br><b>DVAL TESTS</b> |

| <ul> <li>4.1 Board Standalone Tests</li></ul>                                                                                                                                                                                        | 49<br>49<br>51<br>52<br><b>DVAL TESTS</b> |

| 5.3 Product Safety and Reliability Tests | 60 |

|------------------------------------------|----|

| CHAPTER SIX – FUTURE WORKS               | 63 |

| CHAPTER SEVEN – CONCLUSION               | 64 |

| REFERENCES                               | 66 |

## LIST OF FIGURES

| Figure 1.1 Shadowing effect on projector displays                          | 2  |

|----------------------------------------------------------------------------|----|

| Figure 1.2 Sharp's Quattron technology                                     | 2  |

| Figure 2.1 TFT LCD structure                                               | 5  |

| Figure 2.2 Structure of TFT LCD module                                     | 5  |

| Figure 2.3 Backlight structure                                             | 6  |

| Figure 2.4 Operation of LCD                                                | 7  |

| Figure 2.5 Liquid crystals molecular alignment                             | 7  |

| Figure 2.6 Block diagram of TFT-LCD panel T-CON board                      | 10 |

| Figure 2.7 Cold cathode florescent lamp                                    | 12 |

| Figure 2.8 Direct LED BLU (backlight unit) and edge LED BLU                | 13 |

| Figure 2.9 Comparison of the direct LED BLU and edge LED BLU displays      | 14 |

| Figure 3.1 The block diagram of IFPD                                       | 18 |

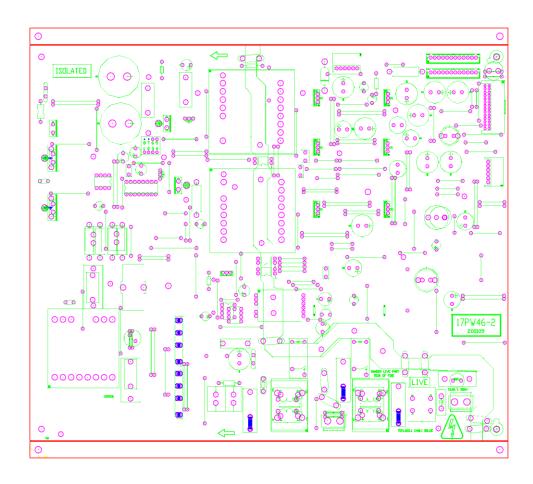

| Figure 3.2 Monitor board top view                                          | 16 |

| Figure 3.3 Monitor board bottom view                                       | 17 |

| Figure 3.4 Chip data path block diagram of RTD2482D                        | 19 |

| Figure 3.5 GND is very thin and there is only one via                      | 22 |

| Figure 3.6 Wrong GND connection                                            | 23 |

| Figure 3.7 Blank plane may act as an antenna                               | 23 |

| Figure 3.8 Mis-connection of two same planes                               | 24 |

| Figure 3.9 PCB top layer                                                   | 25 |

| Figure 3.10 PCB bottom layer                                               | 26 |

| Figure 3.11 (a) Before applying 20H rule (b) After applying 20H rule       | 29 |

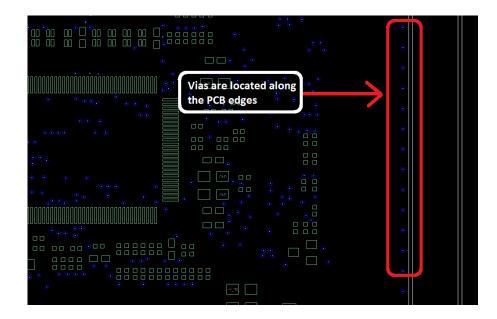

| Figure 3.12 Added vias located at the PCB edges to prevent fringing effect | 29 |

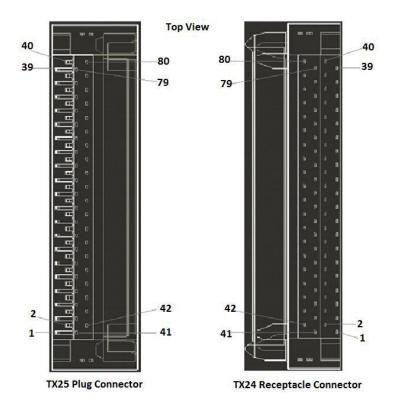

| Figure 3.13 TX24/25 connector pin layout                                   | 35 |

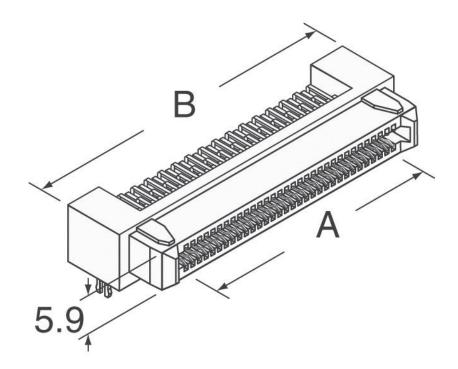

| Figure 3.14 80 pin OPS connector (Docking Side)                            | 36 |

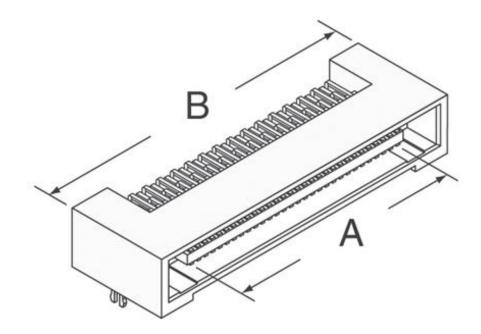

| Figure 3.15 80 pin OPS connector (OPS PC Side)                             | 36 |

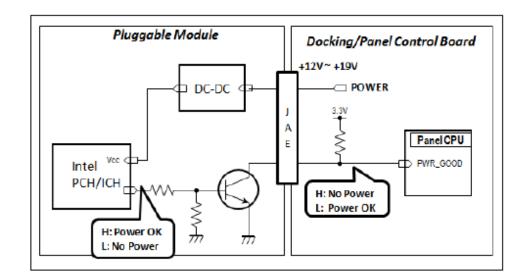

| Figure 3.16 Reference design example for PWR_STATUS                        | 41 |

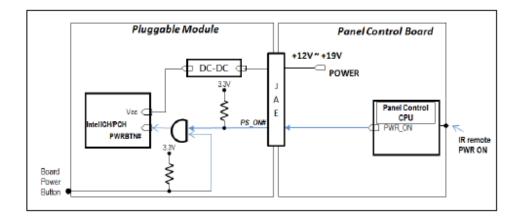

| Figure 3.17 Reference design example for PS_ON#                            | 41 |

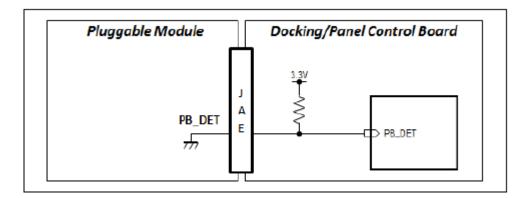

| Figure 3.18 Reference design example for PB_DET                            | 41 |

| Figure 3.19 OPS PC mainboard top view                                      | 42 |

| Figure 3.20 OPS PC mainboard bottom view                                         |

|----------------------------------------------------------------------------------|

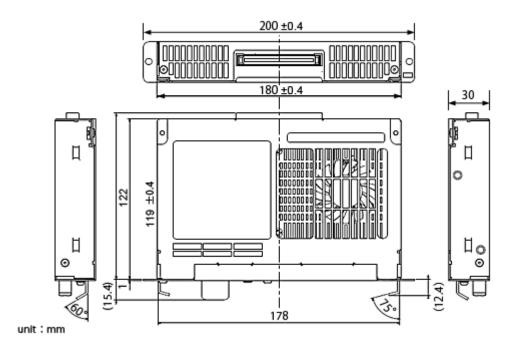

| Figure 3.21 OPS PC mechanical dimensions                                         |

| Figure 3.22 Drawing of the SMPS power board                                      |

| Figure 3.23 Power board top view                                                 |

| Figure 3.24 Infrared touch screen technology                                     |

| Figure 3.25 Configuration of the touch screen PCBs                               |

| Figure 4.1 Power board test block scheme                                         |

| Figure 4.2 Power board test points                                               |

| Figure 4.3 Power board test tool software                                        |

| Figure 4.4 Monitor board test jig                                                |

| Figure 4.5 Monitor board test tool                                               |

| Figure 4.6 Touch screen PCB test jig                                             |

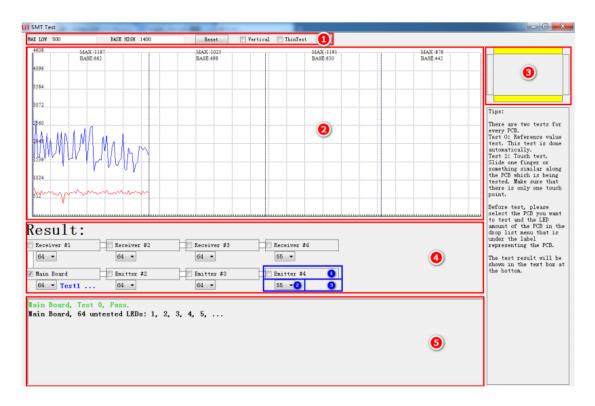

| Figure 4.7 Touch screen PCB test tool                                            |

| Figure 5.1 EMC test phase                                                        |

| Figure 5.2 Radiated emission test at semi-anechoic chamber                       |

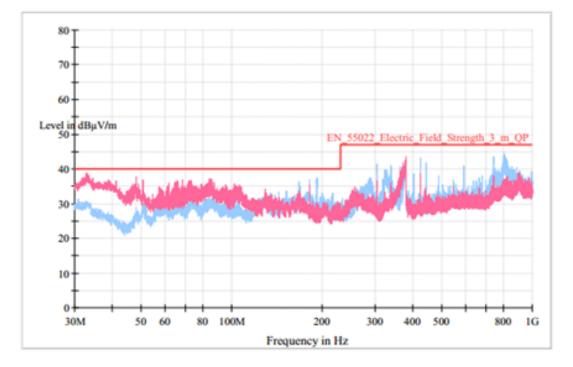

| Figure 5.3 Radiated emission test result                                         |

| Figure 5.4 Radiated immunity tests at full-anechoic chamber                      |

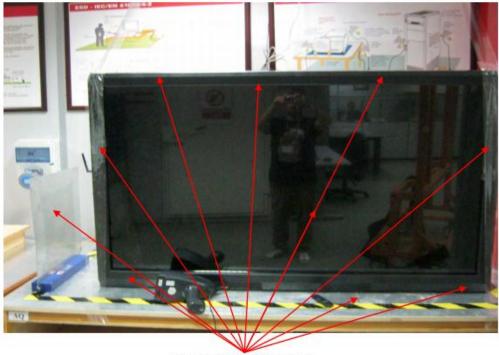

| Figure 5.5 ESD test points, front side of the product                            |

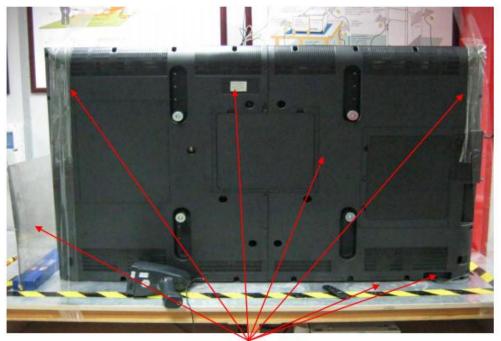

| Figure 5.6 ESD test points, back side of the product                             |

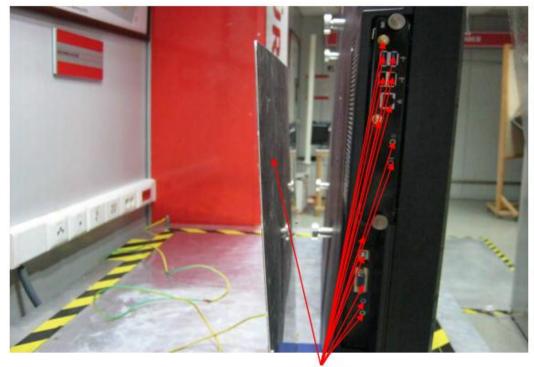

| Figure 5.7 ESD test points, left side of the product                             |

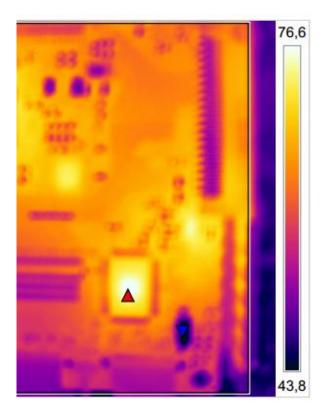

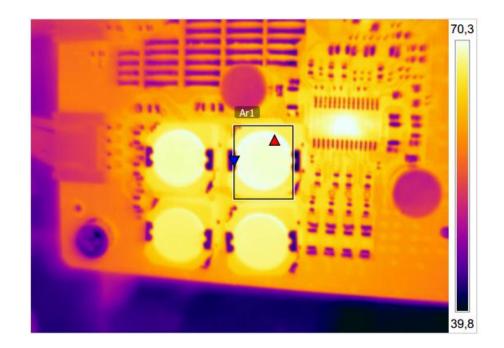

| Figure 5.8 Safety temperature stress test measurement (mainboard scalar IC) 61   |

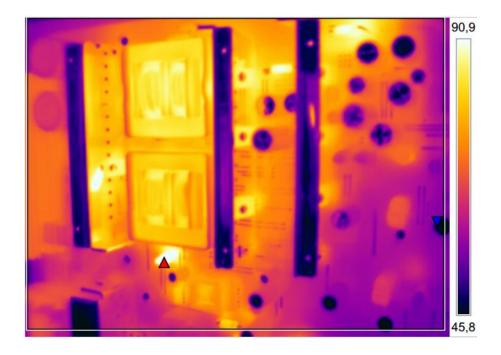

| Figure 5.9 Safety temperature stress test measurement (mainboard audio amplifier |

| and filters61                                                                    |

| Figure 5.10 Safety temperature stress test measurement (power supply unit)       |

## LIST OF TABLES

## Page

| Table 2.1 Comparison between CCFL and LED backlight technologies | . 14 |

|------------------------------------------------------------------|------|

| Table 3.1 OPS PC specification                                   | . 30 |

| Table 3.2 Pin assignment of 80 pin connector                     | . 37 |

| Table 3.3 OPS PC UART signals                                    | . 39 |

| Table 3.4 Control signals of OPS                                 | . 40 |

| Table 3.5 Input specifications of the power board                | . 44 |

| Table 3.6 Output specifications of the power board               | . 44 |

| Table 4.1 Output voltage values for the power board              | . 49 |

| Table 5.1 Radiated emission test result table                    | . 57 |

|                                                                  |      |

## CHAPTER ONE INTRODUCTION

Nowadays, interactive display technology and digital signage technology is a growing market. People are used to use regular billboards to advertise their goods, movies or meals etc. But now, regular billboards are as not prestigious as interactive displays or digital signage.

There are lots of usage area for these types of information displays and digital signage products. They are used at restaurants, shopping malls, stadiums, airports etc. These types of flat panel displays are very good for system integrators since they can be controlled remotely via RS-232 or via Ethernet. Anyone can control power, volume, brightness and even the advertisement content etc. of these products remotely and can get some feedbacks and alarms.

System designers and also advertisers use digital information displays to advertise their customers' goods. For example; we can design a digital signage including a printer and NFC. We can advertise a movie on this digital signage. Anyone can watch the trailer of the movie and take tickets from printer to go this movie by paying the movie tickets with mobile phone NFC feature. This is just an example of usage scenario.

Formerly, projector displays were used for the purposes that mentioned above. But lamps of the projector displays life cycle are around 2000 hours. But the life cycle of TFT-LCD displays is around 35000 hours. Also, there is one another disadvantage of projector displays that some of them have shadowing problems at especially educational systems. On educational systems, there is a touch screen in front of the screen and it provides writing with an opaque object such as a stylus pen or finger. When someone wants to write something on that screen, he/she cuts the reflection of the projector display. In Figure 1.1, shadowing effect can be seen. One another disadvantage of the projector displays is contrast ratio. If someone uses the projector display, he/she needs a dark room in order to provide a better display to the audience.

Figure 1.1 Shadowing effect on projector displays

TFT-LCD (Thin Film Transistor - Liquid Crystal Display) panel displays are used for interactive displays because of the projector's life cycle and shadowing problems. TFT-LCD technology is a growing technology. There are pixels in the TFT-LCD panels. Each pixel is divided in three sub-pixels which are used to give red, green and blue (RGB) colors. But Sharp divides each pixel in four sub-pixels to give red, green, blue and yellow (RGBY) colors and named this technology as Quattron (Figure 1.2).

Figure 1.2 Sharp's Quattron technology

A mainboard is needed to drive the TFT-LCD panel. The interface is LVDS (Low Voltage Differential Signaling) between the TFT-LCD panel display and the mainboard. The LVDS has proven speed, low power, noise control, and cost advantages are popular in point-to-point applications for telecommunications, data communications, and displays.

Intel OPS (Open Pluggable Specification) standard is one of the main focuses for this thesis as well. Since digital signage market is growing, the market is looking for a system that can be managed easily and the product maintenance must be very good. Because these type of products have to work 7/24. Intel OPS standard has a good serviceability and maintainability. Because of these reasons, OPS is the top trend in the market.

The other main topic and challenge for these types of mainboards is approvals. EMC (Electromagnetic Compatibility) and Safety approvals must be taken for these mainboards. At these tests, mainboards are tested according to the IEC EN-60950 and IEC EN-55022.

In this thesis, the aim is to explain the system architecture techniques and details of mainboard design for interactive displays. Thesis' focus is designing an interactive system with all approvals and quality criteria.

## CHAPTER TWO TFT-LCD PANEL DISPLAYS

#### 2.1 A Brief Information about TFT-LCDs

Liquid crystal was discovered by Austrian botanist Fredreich Rheinizer in 1888. In mid 1960s, scientists discovered that applying an external electric charge could change the properties of liquid crystals, i.e., the luminance of light passing through them, and demonstrated the first liquid-crystal display.

TFT-LCD stands for Thin Film Transistor Liquid Crystal Display. TFT LCD is a variant of a liquid-crystal display (LCD) that uses thin-film transistor (TFT) technology to improve image qualities such as addressability and contrast. A TFT LCD is an active-matrix LCD, in contrast to passive-matrix LCDs or simple, direct-driven LCDs with a few segments.

Liquid crystal is the material used as a valve for adjusting the light level for each pixel on the display. TFT is the control circuitry of this liquid crystal material. Depending to the voltage level on each transistor, the liquid crystals control the light level at each sub-pixel. TFT-LCD display is the common name used for display devices using the liquid crystal technology. A thin-film transistor liquid-crystal display (TFT-LCD) is a variant of LCD that offers improved image quality.

TFT LCDs are used in appliances including television sets, computer monitors, mobile phones, handheld video game systems, personal digital assistants, navigation systems and projectors.

#### 2.1.1 TFT LCD Structure

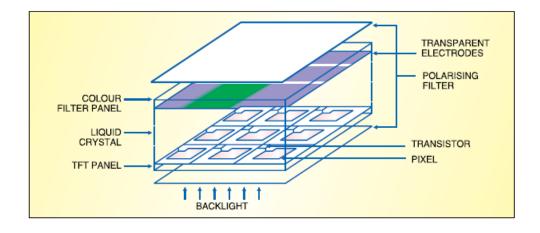

TFT-LCDs have a sandwich-like structure with liquid crystal filled between two transparent glass electrode plates coated with indium tin oxide (ITO) as shown in Figure 2.1 (Figueiredo, 2010).

Figure 2.1 TFT LCD structure (Figueiredo, 2010)

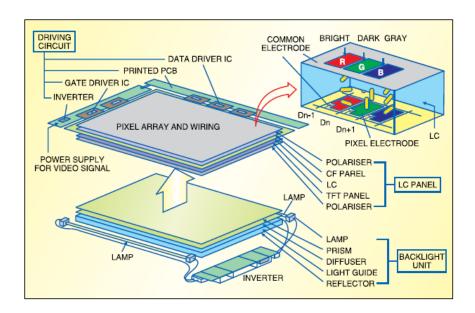

Figure 2.2 shows a color TFT-LCD module. It consists of a TFT-LCD panel, a backlight unit and a driving unit (source driver and gate driver). The TFT-LCD panel has TFTs, liquid crystal, pixel electrodes, storage capacitors and color filter. The color filter has a color resin film containing three primary color pigments (red, green and blue) (Figueiredo, 2010).

Figure 2.2 Structure of TFT LCD module (Figueiredo, 2010)

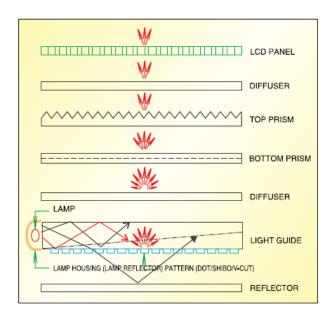

As shown in Figure 2.3, the backlight unit consists of a CCFL lamp with inverter, a light guide panel, a diffuser, and bottom and top prisms. The light guide panel guides the light from the lamp. The diffuser uniformly diffuses the light received from the light guide. The prism concentrates the light and increases the luminance of light up to 1.55 times of the light guide (Figueiredo, 2010).

Figure 2.3 Backlight structure (Figueiredo, 2010)

#### 2.1.2 Working Principle of TFT LCDs

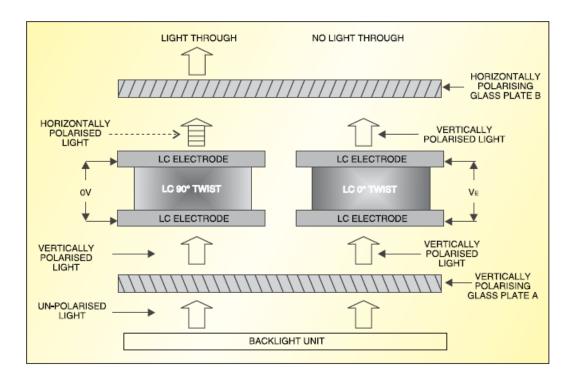

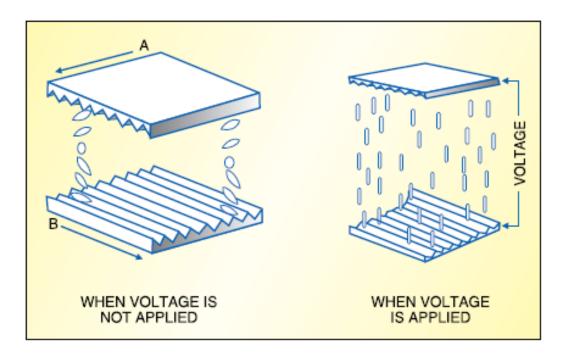

Liquid-crystal molecules are arranged randomly when there is no electric field between ITO electrodes and light is allowed to pass through with molecules twisted by 90°, changing the polarization of light from vertical to horizontal. When an electric field is applied between ITO electrodes, liquid crystal molecules get aligned by removing the 90° twist and light is blocked. When a smaller voltage is applied, the twist is less than 90° and lower intensity light is passed. Thus the applied electric field determines the luminance of light passing through the liquid crystal and various grayscales can be obtained. Figure 2.4 and Figure 2.5 shows the operation of LCDs and liquid crystal molecular alignment (Figueiredo, 2010).

Figure 2.4 Operation of LCD (Figueiredo, 2010)

Figure 2.5 Liquid crystals molecular alignment (Figueiredo, 2010)

#### 2.1.3 Types of TFT LCDs

There are two types of TFT-LCDs: passive-matrix and active-matrix.

A passive-matrix LCD uses one transistor for each row and each column. Each transistor is switched on in sequence and the column transistors are turned on/off according to the image to be displayed. When a transistor is turned off, the respective element or pixel loses its charge and blocks the passage of light. Because of this scanning and the slow response (response time greater than 150ms), passive displays are not very bright and have low contrast ratio. The addressing technique causes crosstalk, which results in blurred images as non-selected pixels are driven through secondary voltage.

An active-matrix LCD uses a separate transistor for each unit pixel. This allows the pixels to stay 'on' longer and thus produce a brighter image. Therefore activematrix LCDs are used in computer monitors, laptops, TVs, mobile screens, etc. (Figueiredo, 2010).

#### 2.1.4 Driving Methods for TFT-LCDs

There are two ways to produce images on a liquid-crystal display: segment driving and matrix driving.

The segment-driving method is mostly used for simple displays, such as segmenttype LCDs that are directly connected to the drivers.

The matrix-driving method is used for high-resolution displays. In this method, displays can be either statically driven or dynamically driven. In the static, or direct, driving method, each pixel is individually wired to the driver. But, as the number of pixels increases, wiring becomes complex. In the dynamic driving method, a voltage is applied at the intersections of specific horizontal scanning electrodes and specific vertical signal electrodes in time-division multiplexing mode using pulse drive (Figueiredo, 2010).

#### 2.1.5 TFT-LCD Panel Controlling and Driving Method

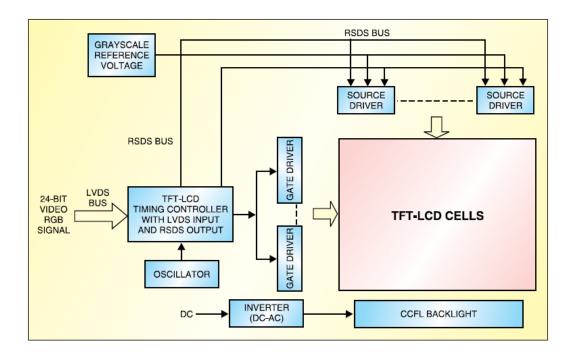

The TFT-LCD controller/driver unit consists of a TFT-LCD timing controller with low-voltage differential signaling (LVDS) receiver, reduced-swing differential signaling (RSDS) transmitter, oscillator, gray-scale reference voltage generator, gate driver, and source or column driver as shown in Figure 2.6.

For large panel size, high resolution and high gray-scale, high-speed data transmission is required between the TFT-LCD timing controller and the source driver. To achieve high-speed data transmission, low-voltage techniques such as mini-LVDS and RSDS having differential voltage of 350mV across the 100-ohm termination resistor at clock frequency of 85 MHz to 170 MHz are used.

The LVDS receiver transfers data serially bit-by-bit over a single pair of wires. This allows fast data transfer with less power consumption. The LVDS receiver receives 24-bit video RGB data and control signal through eight pairs of LVDS channels and two pairs of LVDS clocks. The timing controller generates various control signals to drive the gate driver and the source driver in order to produce images on the screen.

As mentioned earlier, in a TFT-LCD panel, scanning is done line-by-line from top to bottom and each pixel is addressed by selecting the gate line and applying the data signal to TFT-LCD cells through the source driver. The controller generates control signals to address each pixel individually in sync with the gate driver and source driver and, at the same time, the RGB video signal is passed through the source driver to TFT-LCD cells. The gray-scale reference generator generates reference voltages to convert the digital RGB signal into analogue RGB signal using either a voltage divider or DC-DC converter. The gate driver selects the TFTs by applying a positive pulse to the gate of TFTs in a specific row and thus allows line-by-line scanning from top to bottom.

Figure 2.6 Block diagram of TFT-LCD panel T-CON board (Figueiredo, 2010)

The source driver consists of a shift register, data latch, level shifter, digital-toanalogue converter (DAC) and output buffer.

Digital data is loaded and stored in data latches until conversion takes place. Because each output has an independent DAC, data conversion is required only once per line. The DAC converts the digital gray-scale value into an equivalent analogue voltage with very fast conversion rate and this analogue voltage is fed to TFT-LCD cells through the output buffer.

The DAC also allows gamma correction. In a TFT-LCD, TFTs are used to control on/off state of the displayed pixel. But this on/off function is insufficient to display images correctly. Gamma correction is essential because the image is either breached out or too dark. It controls the overall brightness of images displayed on the screen (Figueiredo, 2010).

#### 2.1.6 Gray-scale and Color Generation

The luminance of light depends on the voltage applied between the two transparent electrodes of a liquid crystal. Gray levels are an intermediate level of brightness between the brightest of bright and the darkest of dark that a unit pixel can generate by varying the voltage between the electrodes. This gray-scale voltage can be generated either in analogue or digital form. Gray-scale voltage in analogue form, i.e., continuous range, is generated using a voltage divider. The DC-DC converter can also be used to obtain in-between voltages for gray-scale generation.

In the digital method, grayscale voltage is defined in 8-bit, 10-bit and 12-bit forms. Hence the number of gray levels is determined by the number of bits used to represent the gray-scale voltage. For example, if eight bits are used to represent gray-scale voltage, the number of possible gray levels will be  $2^8$  (= 256). The color filter of a TFT-LCD consists of three primary colors: red, green and blue. In a color TFT-LCD, each pixel is a combination of three sub-pixels having red (R), green (G) and blue (B) colors. Because the sub-pixels are too small to distinguish them independently, practically any color produced is a mixture of these primary colors. The video signal is composed of R, G and B color signals and 'n' bits are used to represent each color. The number of colors produced is determined by the combinations of R, G and B that are possible with the number of gray-scale levels: If an LCD displays images with 8-bit gray-scale, it will display  $2^8$  (=256) shades for red, green and blue color each. Thus the total number of different colors, known as True Color, is  $2^8 \times 2^8 \times 2^8$  (=16.78 million).

If you compare 8- and 10-bit grayscale displays, you'll find that 10-bit gray-scale images are softer and more natural than 8-bit gray-scale images. This is because 10-bit gray-scale gives  $2^{10}$  (=1024) shades for each primary color and the total number of colors (natural colors) is  $2^{10} \times 2^{10} \times 2^{10}$  (=1.07 billion). A 12-bit gray-scale has also been tried. It gives much more realistic picture (Figueiredo, 2010).

#### 2.2 Backlight Technology of TFT-LCD Panels

There are two backlight technologies that are commonly used all over the world.

- CCFL (Cold Cathode Florescent Lamp) Backlight Technology

- LED Backlight Technology

#### 2.2.1 CCFL Backlight Technology

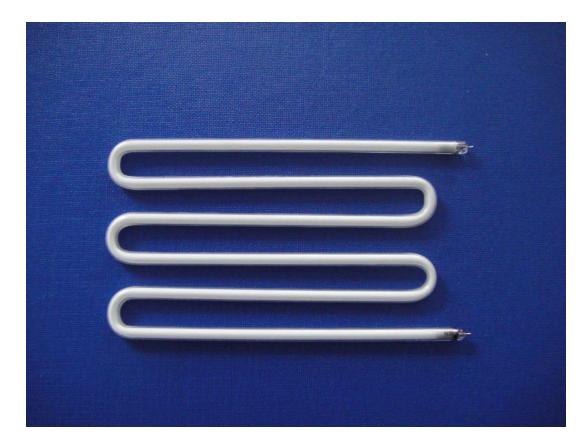

CCFL's are an older technology, and for the moment are the most widely used backlights in laptops LCDs. They consist of a fluorescent tube connected to a voltage inverter board which provides power to the backlight. Sometimes the backlight contains 2 tubes along with 2 pairs of inverters; these are called "Dual Backlights" or 2-CCFL. CCFL backlight unit can be seen in Figure 2.7 below.

Figure 2.7 Cold cathode florescent lamp

#### 2.2.2 LED Backlight Technology

LED backlight technology is a newer technology than CCFL. There are two designs for LED backlight technology.

- Edge LED Backlight

- Direct LED Backlight

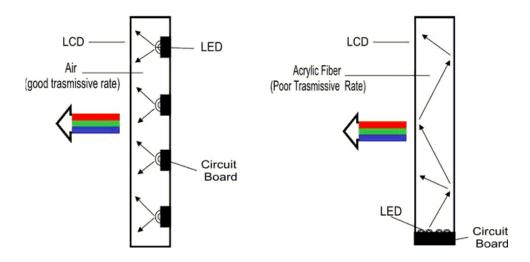

There are some advantages and disadvantages if we compare these two types. For example TFT-LCD panels that are using direct LED backlight are thicker than the panels that are using edge LED backlight (Figure 2.8). But contrast ratios of direct LED backlight panels are better than edge LED backlight panels. This contrast difference can be seen in Figure 2.9.

Figure 2.8 Direct LED BLU (backlight unit) and edge LED BLU

Figure 2.9 Comparison of the direct LED BLU and edge LED BLU displays

### 2.2.3 Comparison of CCFL and LED Backlight Technologies

There is a comparison table between CCFL and LED backlight technologies below in Table 2.1.

|            | CCFL                                         | LED                                            |

|------------|----------------------------------------------|------------------------------------------------|

| Size       | Thicker and heavier                          | Thinner and lighter                            |

| Cost       | Cheaper and more cost effective              | Affordable cost                                |

| Power      | Higher power consumption and heat generation | Lower power consumption<br>and heat generation |

| Brightness | Lower brightness                             | Generally higher brightness                    |

| Finish     | Available in Matte or Glossy                 | Available in Matte or Glossy                   |

| Lifespan   | Shorter lifespan                             | Longer lifespan                                |

Table 2.1 Comparison between CCFL and LED backlight technologies

## CHAPTER THREE SYSTEM DESIGN

The system has several boards including power board, monitor board, touch controlled control board and OPS board. The system has also a TFT LCD panel with LED backlight technology. The main reason behind choosing a LED backlight LCD panel is that they have a long life time (about 35000 hours working time). Also they have a good video quality (1.07 billion color depth).

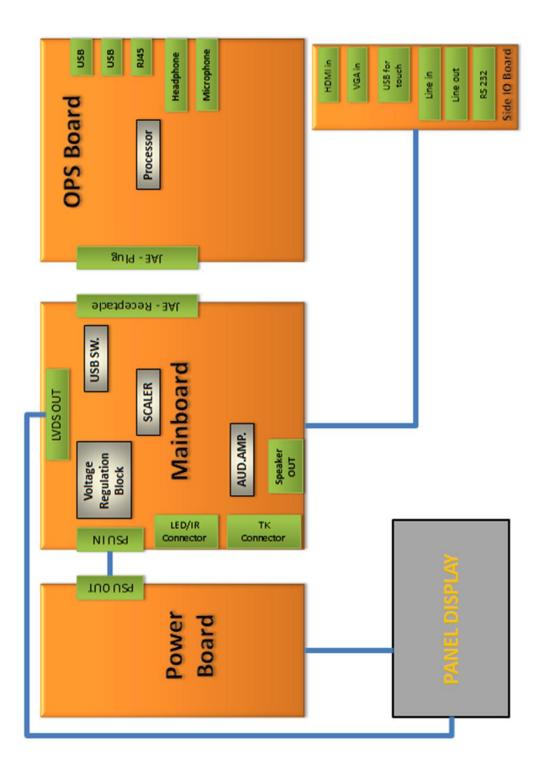

In this chapter, each board will be explained in detail. The block diagram of the system can be seen below as well.

#### **3.1 Monitor Board Design**

#### 3.1.1 Schematics Design

In this chapter, the design techniques and details of monitor board design for interactive displays will be explained.

The monitor board is called 14MON02. This monitor board is designed to drive the TFT-LCD panel and to control all other peripherals such as touch screen, key buttons, LED IR remote controller receiver, speakers and side I/O board. The specification of the monitor board is as listed below;

- FHD panel driving capability

- Control buttons

- VGA input

- HDMI input

- USB B Type (to connect touch screen to external sources)

- Line in

- Line out

- Remote controller support

- 30W audio output support

- OPS 80 Pin Connector Interface (to connect OPS MBs)

• RS232 for remote management (optional)

Firstly, the designer should freeze the specification of the board. Then, a block diagram should be drawn in order to clarify all blocks of the schematics and design.

Figure 3.2 Monitor board top view

Figure 3.3 Monitor board bottom view

#### 3.1.1.1 Scalar Block

Realtek Semiconductor RTD2482D has been selected as main IC in this project. This IC is called display scalar IC as well. RTD2482D has an embedded microcontroller unit inside. So, we do not need any other microcontroller to control other parts of the mainboard. The features of RTD2482D are briefly explained below.

- RGB input

- YPbPr input

- HDMI input

- DVI input

- Embedded MCU

- Embedded Audio DAC

- 1920x1200 and 1920x1080 resolution support

Figure 3.1 Block diagram of IFPD

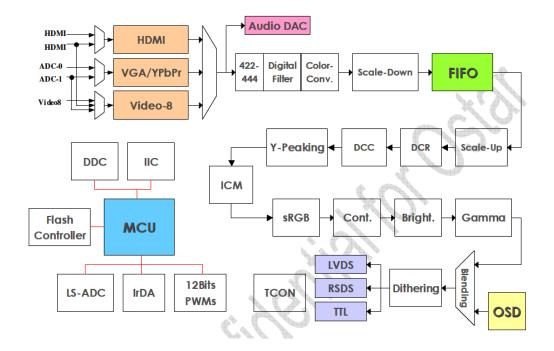

*3.1.1.1.1 Features of RTD2482D.* The Realtek RTD2482D is an advanced all-inone LCD monitor controller with analog (RGB), YPbPr, HDMI, DVI, and DisplayPort 2A+2H inputs. It includes a Microcontroller Unit (MCU), an audio DAC, an advanced 6-axis color engine by VividColor, and an infrared controller, providing a powerful and integrated cost-effective platform supporting up to 1920x1200/1920x1080 (1080p Full HD) resolution. The internal block diagram of RTD2482D can be seen in Figure 3.4 below.

The full-featured RTD2482D is a Frame-Buffer-Less solution offering a low-cost system design by reducing the number of system components, and by deploying on a 2-layer PCB.

Figure 3.4 Chip data path block diagram of RTD2482D

#### 3.1.1.2 Power Block

2 voltage regulators and 2 low dropout linear regulators has been used for power block. Texas Instruments TPS54229 is used as voltage regulator and LM1117 is used as LDO. There are three voltages that are supplied by power board. These are 24V for audio and backlight, 12V and 13V for standby.

*3.1.1.2.1 TPS54229 Synchronous Buck Converter*. The TPS54229 is an adaptive on-time synchronous buck converter. The TPS54229 also has a proprietary circuit that enables the device to adapt to both low ESR output capacitors, such as POSCAP or SP-CAP, and ultra-low ESR ceramic capacitors. The device operates from 4.5V to 18V input. The output voltage can be programmed between 0.76V and 7V. At this project, it is used to convert 12V to 5V and also 3.3V.

3.1.1.2.2 LM1117 Low Dropout Regulator. The LM1117 is a series of low dropout voltage regulators with a dropout of 1.2V at 800mA of load current. The designer can adjust the output, or some versions of LM1117 have fixed output. For this LDO, minimum 10uF tantalum capacitor is required at the output to improve the transient response and stability.

At this project, LM1117 is used for 3.3V to 1.2V conversion and also 5V to 3.3V conversion.

#### 3.1.1.3 Audio Block

Texas Instruments TPA3118D2 is used for this project. TPA3118D2 is a class-D audio amplifier. The high efficiency of the TPA3118D2 allows designer to use 2x15W output without external heat sink on a single layer PCB.

The advanced oscillator/PLL circuit inside TPA3118D2 employs a multiple switching frequency option to avoid AM interferences. This is achieved together with an option of Master/Slave option, making it possible to synchronize multiple devices.

The TPA3118D2 is fully protected against faults with short circuit protection and thermal protection as well as over voltage, under voltage and DC protection. Faults are reported back to the processor to prevent devices from being damaged during overload conditions.

At this project 8 ohm 15W speakers are used as load. Also the gain is set to 26dB. The input of the TPA3118D2 is 24V. Also, as performance quality criteria, maximum %10 total harmonic distortion is allowed.

#### 3.1.1.4 USB Switch

Texas Instruments TS3USB221 is used for this project. The TS3USB221E is a high-bandwidth switch specially designed for the switching of high-speed USB 2.0 signals in handset and consumer applications, such as cell phones, digital cameras, and notebooks with hubs or controllers with limited USB I/Os. The wide bandwidth (1 GHz) of this switch allows signals to pass with minimum edge and phase distortion. The device multiplexes differential outputs from a USB host device to one of two corresponding outputs. The switch is bidirectional and offers little or no attenuation of the high-speed signals at the outputs. It is designed for low bit-to-bit skew and high channel-to-channel noise isolation, and is compatible with various standards, such as high-speed USB 2.0 (480 Mbps).

The TS3USB221E integrates ESD protection cells on all pins, is available in a SON package (3 mm  $\times$  3 mm) as well as in a tiny mQFN package (2 mm  $\times$  1.5 mm) and is characterized over the free air temperature range from -40°C to 85°C.

The aim of using the USB switch IC is that the 14MON02 allows that user can use the product as All-in-One PC or just a monitor with touch screen feature since the product is interactive. When user use the product as AIO PC, then USB switch is switching the touch screen USB signals to the OPS PC. When user use the product as a touch monitor, then USB switch is switching the touch screen USB signals to the external PC. SON (small-outline no lead) package is used.

#### 3.1.2 Layout Design

For layout design, 2-layer PCB structure has been chosen because of the cost varieties. But for 2-layer PCB, it is hard to pass EMC tests easily. Because of the EMC issues, the designer should check every high speed signals.

Even though the designer should check high speed signals, the designer should also check the voltage nets that related net can carry required current or not. The designer should also check the impedance matching and length matching of the nets. Crosstalk, signal reflections and signal stubs are other issues. The designer has to prevent these issues. There are some examples about layout review below.

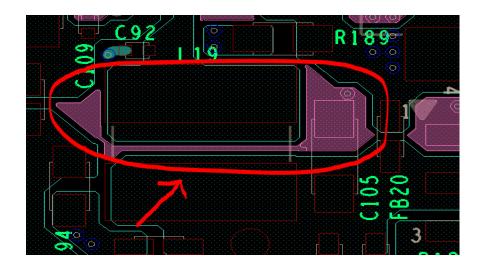

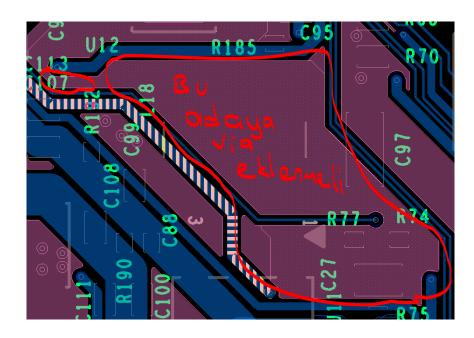

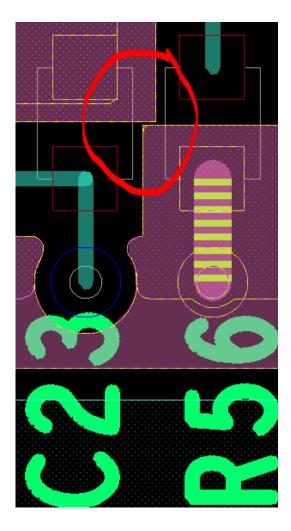

As shown in Figure 3.5 below, GND plane connected to the GND with only one via. Make the L19 pad connections thinner and make the GND thicker. Then add some more vias.

Figure 3.5 GND is very thin and there is only one via

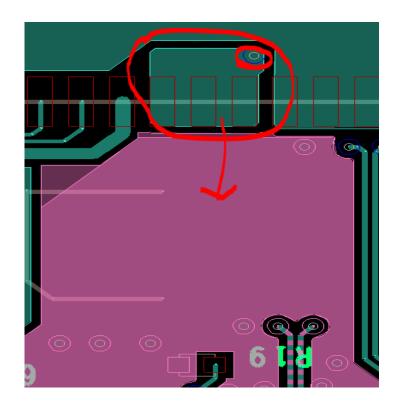

As shown in Figure 3.6 below, the GND plane in the circle is connected to the GND in a far place with via. Delete via and connect it to the GND as seen below the circle.

Figure 3.6 Wrong GND connection

Add some vias to the plane shown below in Figure 3.7. Because this plane may act as an antenna.

Figure 3.7 Blank plane may act as an antenna

4) Connect these two GND plane shown in Figure 3.8.

Figure 3.8 Mis-connection of two same planes

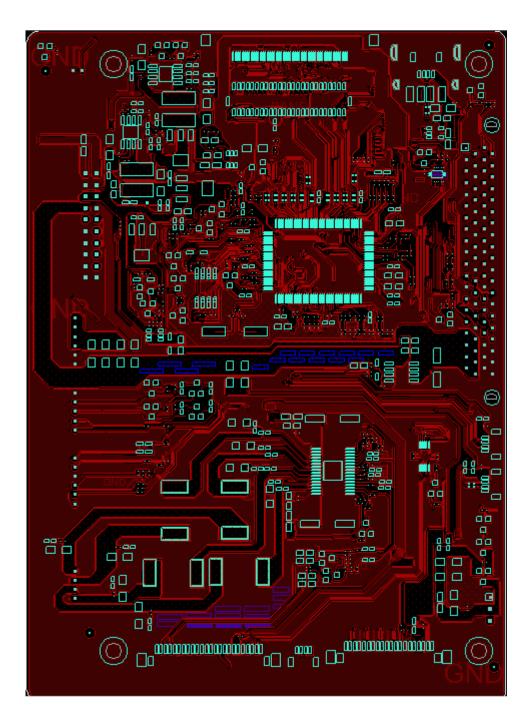

The top view and the bottom view of layout design of the monitor board can be seen in Figure 3.9 and Figure 3.10 respectively below.

Figure 3.9 PCB top layer

Figure 3.10 PCB bottom layer

I would like to add some rules, which are explained by Dr. Eric Bogatin who is a physicist and has an excellent knowledge about signal integrity, about designing a PCB by caring the EMC.

- 1) Critical nets must not cross a split in the adjacent reference plane.

- 2) Critical nets must not change reference planes.

- Critical nets may not be within a specified distance of the edge of their reference plane.

- 4) Critical nets may not be routed within a specified distance from an I/O net.

- All critical nets must be buried between solid planes. The allowable length of the exposed portion of a critical net may be specified.

- All critical nets must have a "ground-guard" trace on either side of the critical net.

- All differential critical nets must have a "ground-guard" trace on either side of the differential pair of nets.

- 8) All differential critical nets must be routed within a specified distance of each other, and the length of the differential pair of nets must match within a specified amount.

- 9) All power and ground traces longer than a specified distance must be wider than another specified distance. This does not include grounded guard traces.

- 10) Decoupling capacitors must be placed between all adjacent plane pairs within a specified grid density.

- 11) A decoupling capacitor must be connected between the power and groundreference planes and be placed within a specified distance from each IC power pin.

- 12) The trace connecting between the IC power and/or ground reference pin to the associated via to the power/ground-reference plane must be no longer than the specified distance.

- 13) The trace connecting between a decoupling capacitor to the associated via to the power/ground-reference plane must be no longer than the specified distance.

- 14) All power and ground-reference traces longer than a specified length must have a decoupling capacitor within a specified distance from the IC power pin.

- 15) All I/O filters must be placed within a specified distance from the I/O connector.

- 16) All oscillators must be placed within a specified distance from the clock driver (or other device) that they drive.

There is also another rule about PCB design called H-20H rule. This will be explained in next section.

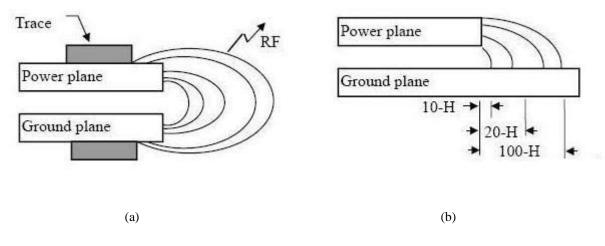

### 3.1.2.1 20H Rule at PCB Design

The 20-H rule, first proposed by W. Michael King and described in the book by Mark I. Montrose, is a design guideline for laying out printed circuit boards with power and ground planes. The rule states that the edges of the power plane should be set back from the edges of the ground plane by a distance equal to 20 times the vertical spacing between the planes. The idea behind this rule is that fringing fields around the edge will be better contained. It has also been suggested that the radiation from this geometry will be lower compared to the radiation from a board where both planes are the same size.

Use of the 20-H rule increases the intrinsic self-resonant frequency of the PCB, because the physical dimensions of the power distribution network are altered. Since less capacitance will be present, there will be a higher self-resonant frequency of operation. Assume that the termination value is about ten times higher than the characteristic impedance of the transmission line. In this situation, however, the "termination" is a value that will not fully terminate the line. The position of the termination is such that a rather long "stub," as compared to the total transmission line length, is created at the end of the line. The fringing of the flux fields depends on the exact relationship and distribution path near the plane edges. The distribution of

the flux depends on the geometry of the component and its distance from the edge of the PCB.

Figure 3.11 (a) Before applying 20H rule (b) After applying 20H rule

To avoid this fringing effect at the edges of the PCB, there must be some distance between the edges of GROUND and POWER planes of the PCB. If the gap between GROUND and POWER plane is H, then the distance between the edges of these two planes must be minimum 20H.

There is another way to avoid this fringing effect on the PCB edges. To avoid this effect, the designer may also add vias along the PCB edges.

Figure 3.12 Added vias located at the PCB edges to prevent fringing effect

### 3.2 OPS (Open Pluggable Specification) Board and Interface

The Open Pluggable Specification (OPS) helps standardize the design and development of digital signage devices and pluggable media players. Intel created OPS to address digital signage market fragmentation and simplify device installation, usage, maintenance, and upgrades.

The OPS involves the integration concept of a Pluggable Module into the display panel thru a single and standard interfacing based on the 80 pin JAE plug and receptacle connectors as seen on the figures below. The power supply to the Pluggable Module together with the defined feature interfaces are being routed through this set of connectors to provide a functional system level computing solution for digital signage. Specification of the OPS PC is shown in Table 3.1 below.

| Feature        | Item         | Description                                                                                                                                                                         |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor      | CPU          | Intel Ivy Bridge 3rd Generation Mobile Processor<br>Support (Core i3, Core i5, Core i7) (PGA Type)                                                                                  |

| Chipset        | I/O          | Intel 7-series (Panther Point) Chipset                                                                                                                                              |

| Memory         | Туре         | 2 x 204 pin SO-DIMM socket, support up to DDR3<br>1600MHz with un-buffered and Non-ECC memory<br>module up to 16GB per SO-DIMM                                                      |

| Super IO       | SIO          | 1 x Super IO Chip                                                                                                                                                                   |

| Graphics       | Graphic Chip | Integrated GPU, Intel HD Graphics 4000 with 512MB memory support                                                                                                                    |

| OPS<br>Signals | Interface    | <ul> <li>1 x TMDS signal to JAE TX25 80 pin connector</li> <li>1 x DP signal to JAE TX25 80 pin connector</li> <li>1 x LAN controller support 10/100/1000M</li> <li>DASH</li> </ul> |

| Audio          | HD Audio     | Input: Mic in Output: Line out                                                                                                                                                      |

| Table 3.1 | OPS PC | specification |

|-----------|--------|---------------|

|-----------|--------|---------------|

Table 3.1 OPS PC specification (continue)

| Feature     | Item | Description                                                 |

|-------------|------|-------------------------------------------------------------|

|             |      | 1 x 22 pin SATA right angle connector for slide in          |

| Storage     | SATA | 2.5" SATA HDD/SDD                                           |

|             |      | 1 x Mini PCIe connector for mSATA (optional)                |

|             |      | -USB 3.0 port 1~2 on the front panel                        |

|             |      | -USB 2.0 port 3~4 on the front panel(inculding              |

|             |      | USB3.0)                                                     |

| USB Signals |      | -USB 2.0 port 5~7 on the JAE TX25 pin plug                  |

|             |      | connector                                                   |

|             |      | -USB 2.0 port 8 on board pin-header                         |

|             |      | -USB 2.0 port 9 on the mini-PCIe connector                  |

|             |      | 1 - DWD STATUS signal to LAE TV25.90 sin shus               |

|             |      | 1 x PWR_STATUS signal to JAE TX25 80 pin plug               |

|             |      | connector, This pin shall be open collector and pull up     |

|             |      | to 3.3V on docking board side.                              |

|             |      | 1 x PS_ON# signal to JAE TX25 80 pin plug                   |

|             |      | connector, OPS module shall not exceed 200ms for            |

|             |      | PS_ON# timing spec.                                         |

| Control     |      | 1 x PB_DET signal to JAE TX25 80 pin plug                   |

| Signals     |      | connector, High: No pluggable, LOW: Pluggable               |

|             |      | board present None CEC function                             |

|             |      | 1 x SYS_Fan signal to JAE TX25 80 pin plug                  |

|             |      | connector, High: system fan off, low: system fan on         |

|             |      | 1 x ATX_PWRON <sup>[1]</sup> signal to Pin41 of JAE TX25-80 |

|             |      | connector                                                   |

|             |      | 1 x WAKE# <sup>[1]</sup> signal to Pin42 of JAE TX25-80     |

|             |      | connector                                                   |

|             |      |                                                             |

|             |      | <sup>[1]</sup> Signal names may change.                     |

|             |      |                                                             |

Table 3.1 OPS PC specification (continue)

| Feature           | Item                                    | Description                                            |

|-------------------|-----------------------------------------|--------------------------------------------------------|

|                   |                                         | Standby power consumption must be less than 1W.        |

|                   |                                         | Standby power consumption must be less than 1W.        |

|                   |                                         | 1 x 3pin CPU fan connector, support smart fan          |

|                   |                                         | function (CPU fan's noise will not exceed 30dB at      |

|                   |                                         | max RPM)                                               |

|                   |                                         | Wake On LAN and PXE boot support                       |

|                   |                                         | DASH support                                           |

|                   |                                         | UART communication with OPS SIO for power              |

| Other             |                                         | modes (S3, S4, S5 etc.)                                |

| Features          |                                         | OPS must be compliant with EMC (2004/108/EC)           |

|                   |                                         | and low voltage (2006/95/EC) regulations according     |

|                   |                                         | to EN 60950-1:2006, EN 55022:2006 + A1: 2007, EN       |

|                   |                                         | 55024:1998+A1:2001+A2:2003, EN 61000-3-2:2006          |

|                   |                                         | and EN 61000-3-3:1995+A1:2001+A2:2005 or TS            |

|                   |                                         | EN 60950-1: 2008, TS EN 55022: 2009 + A1: 2009,        |

|                   |                                         | TS EN 55024: 1998 + IS1: 2008, TS EN 61000-3-2:        |

|                   |                                         | 2010 and TS EN 61000-3-3: 2005 + A2: 2006              |

|                   | · · • • • • • • • • • • • • • • • • • • | 1 x mini-PCIe full & half size slot, support Wireless  |

| Expansion         | mini-PCIe                               | LAN, and TV-Tuner                                      |

| Watahdaa          |                                         | Watchdog timeout can be programmable by Software       |

| Watchdog<br>Timer |                                         | from 1 second to 255 seconds and from 1 minute to      |

| 1 111101          |                                         | 255 minutes                                            |

|                   |                                         | $+12V \sim +19V \pm \%15$ wide range DC Input from JAE |

|                   |                                         | TX25 80 pin plug connector                             |

| Power Input       |                                         | The in-rush current spec for the OPS module shall not  |

|                   |                                         | exceed 10A to ensure smooth power delivery form        |

|                   |                                         | the display panel PSU                                  |

| Table 3.1 OPS PC specification ( | continue) |

|----------------------------------|-----------|

|----------------------------------|-----------|

| Feature | Item       | Description                                             |

|---------|------------|---------------------------------------------------------|

|         |            | USB Redirection                                         |

|         |            | Boot control                                            |

|         |            | Hardware Information Management (CPU, Fan               |

|         |            | System Memory etc.)                                     |

|         |            | Physical Asset                                          |

|         |            | Power State Management – Remote Control                 |

|         |            | • Sensors                                               |

|         |            | BIOS Management                                         |

|         |            | Text Console Redirection                                |

| DASH    | Required   | • Log profile                                           |

| DASH    | features   | Software Inventory                                      |

|         |            | Opaque Management Data                                  |

|         |            | Software-Firmware Update                                |

|         |            | • OS Status                                             |

|         |            | Alert Indication                                        |

|         |            | Account Management                                      |

|         |            | Role Management                                         |

|         |            | Network Configuration                                   |

|         |            | • Generating a syslog for temperature, storage info and |

|         |            | alerts                                                  |

|         |            | 1 x RJ45 with LEDs for Gigabit LAN                      |

|         |            | 2 x USB 2.0 (USB connectors must be on a seperate       |

|         |            | small board and connected to MB with a board-to-        |

| Input & |            | board connector)                                        |

| Output  | Front I/Os | 2 x USB 3.0 (USB connectors must be on a seperate       |

| Ports   |            | small board and connected to MB with a board-to-        |

|         |            | board connector)                                        |

|         |            | 1 x Mic in phone jack                                   |

|         |            | 1 x Line out phone jack                                 |

Table 3.1 OPS PC specification (continue)

| Feature      | Item       | Description                                      |

|--------------|------------|--------------------------------------------------|

|              |            | 1 x TMDS signal                                  |

|              |            | 1 x DP signal                                    |

| Input &      | JAE 80 pin | 2 x USB 2.0 signal                               |

| Output Ports | I/Os       | 1 x USB 3.0 signal                               |

|              |            | 1 x Audio out L/R signal                         |

|              |            | 1 x RX/TX 3.3V (UART)                            |

|              |            | DC +12V~+19V input                               |

|              |            |                                                  |

| On Board     |            | 1 x External Li-ion Battery                      |

| RTC          |            | Operating Temperature: 0~50°C                    |

|              |            | Storage Temperature: -20~80°C                    |

| Environment  |            |                                                  |

| Conditions   |            | Operating Relative Humidity(Non-condensing): 90% |

|              |            | ROHS                                             |

|              |            |                                                  |

### 3.2.1 80 Pin OPS Connector

The connector used for the Pluggable Module and the docking board interconnect is based on the JAE TX24/TX25 family of plug and receptacle connectors. The JAE connector pins are capable of supporting up to a maximum current of 1A. For details refer to the JAE connector datasheet or contact a JAE representative. The 80-pin right angle blind mate plug connector (p/n: TX25-80P-LT-H1E) and its receptacle (p/n: TX24-80R-LT-H1E) provide interfacing for the following features:

Power: DC IN +12V~+19V @ 8A max

Display Interface: DVI-D/TMDS and Display Port

Audio: Left and Right Channel

USB: 3\*USB 2.0 (when USB3.0 is not used) or 2\*USB 2.0 and 1\*USB 3.0

UART: Serial communication (TX and RX only)

Control Signals: Pluggable Module Power Status, Power ON via display panel, Pluggable Board Detect, Consumer Electronics Control (CEC), and System Fan Control.

#### 3.2.1.1 Pin Assignment of 80 Pin Connector

The JAE connector pin definition and assignment with regards to the features are listed in Table 3.2. Pin mapping indicated was based on the placement on the connector from top view as indicated in Figure 3.13.

Figure 3.13 TX24/25 connector pin layout

Figure 3.14 80 pin OPS connector (Docking Side)

Figure 3.15 80 pin OPS connector (OPS PC Side)

| Pin<br>No | Signal    | Description  | I/O | Pin<br>No | Signal           | Description | I/O |

|-----------|-----------|--------------|-----|-----------|------------------|-------------|-----|

| 1         | DDP_3N    | Display Port | 0   | 21        | TMDS0+           | DVI-D       | 0   |

| 2         | DDP_3P    | Display Port | 0   | 22        | GND              | Ground      | -   |

| 3         | GND       | Ground       | -   | 23        | TMDS1-           | DVI-D       | 0   |

| 4         | DDP_2N    | Display Port | 0   | 24        | TMDS1+           | DVI-D       | 0   |

| 5         | DDP_2P    | Display Port | 0   | 25        | GND              | Ground      | -   |

| 6         | GND       | Ground       | -   | 26        | TMDS2-           | DVI-D       | 0   |

| 7         | DDP_1N    | Display Port | 0   | 27        | TMDS2+           | DVI-D       | 0   |

| 8         | DDP_1P    | Display Port | 0   | 28        | GND              | Ground      | -   |

| 9         | GND       | Ground       | -   | 29        | DVI_DDC_D<br>ATA | DVI-D       | 0   |

| 10        | DDP_0N    | Display Port | 0   | 30        | DVI_DDC_C<br>LK  | DVI-D       | 0   |

| 11        | DDP_0P    | Display Port | 0   | 31        | DVI_HPD          | DVI-D       | 0   |

| 12        | GND       | Ground       | -   | 32        | GND              | Ground      | -   |

| 13        | DDP_AUXN  | Display Port | I/O | 33        | +12V~+19V        | Power       | -   |

| 14        | DDP_AUXP  | Display Port | I/O | 34        | +12V~+19V        | Power       | -   |

| 15        | DDP_HPD   | Display Port | Ι   | 35        | +12V~+19V        | Power       | -   |

| 16        | GND       | Ground       | -   | 36        | +12V~+19V        | Power       | -   |

| 17        | TMDS_CLK- | DVI-D        | 0   | 37        | +12V~+19V        | Power       | -   |

| 18        | TMDS_CLK+ | DVI-D        | 0   | 38        | +12V~+19V        | Power       | -   |

| 19        | GND       | Ground       | -   | 39        | +12V~+19V        | Power       | -   |

| 20        | TMDS0-    | DVI-D        | 0   | 40        | +12V~+19V        | Power       | -   |

Table 3.2 Pin assignment of 80 pin connector

| Pin<br>No | Signal     | Description | I/O | Pin<br>No | Signal     | Descriptio<br>n                   | I/O       |

|-----------|------------|-------------|-----|-----------|------------|-----------------------------------|-----------|

| 41        | RSVD       | Reserved    | -   | 61        | USB_PP2    | USB                               | I/O       |

| 42        | RSVD       | Reserved    | -   | 62        | GND        | Ground                            | -         |

| 43        | RSVD       | Reserved    | -   | 63        | USB_PN1    | USB                               | I/O       |

| 44        | RSVD       | Reserved    | -   | 64        | USB_PP1    | USB                               | I/O       |

| 45        | RSVD       | Reserved    | -   | 65        | GND        | Ground                            | -         |

| 46        | RSVD       | Reserved    | -   | 66        | USB_PN0    | USB                               | I/O       |

| 47        | RSVD       | Reserved    | -   | 67        | USB_PP0    | USB                               | I/O       |

| 48        | RSVD       | Reserved    | -   | 68        | GND        | Ground                            | -         |

| 49        | RSVD       | Reserved    | -   | 69        | LINEOUT_L  | Audio-Lch                         | 0         |

| 50        | SYS_FAN    | Fan Control | 0   | 70        | LINEOUT_R  | Audio-Rch                         | 0         |

| 51        | UART_RXD   | UART 3.3V   | Ι   | 71        | CEC        | Consumer<br>Electronic<br>Control | I/O       |

| 52        | UART_TXD   | UART 3.3V   | 0   | 72        | PB_DET     | Pluggable<br>Board<br>Detect      | 0         |

| 53        | GND        | Ground      | -   | 73        | PS_ON#     | Pluggable<br>Signal ON            | Ι         |

| 54        | StdA_SSRX- | USB3.0      | Ι   | 74        | PWR_STATUS | Power Good                        | 0<br>(OC) |

| 55        | StdA_SSRX+ | USB3.0      | Ι   | 75        | GND        | Ground                            | -         |

| 56        | GND        | Ground      | -   | 76        | GND        | Ground                            | -         |

| 57        | StdA_SSRX- | USB3.0      | Ι   | 77        | GND        | Ground                            | -         |

| 58        | StdA_SSRX+ | USB3.0      | Ι   | 78        | GND        | Ground                            | -         |

| 59        | GND        | Ground      | -   | 79        | GND        | Ground                            | -         |

| 60        | USB_PN2    | USB         | I/O | 80        | GND        | Ground                            | -         |

Table 3.2 Pin assignment of 80 pin connector (continue)

### 3.2.2 OPS Signals Description

There are some important signals that should be explained. These signals are UART signals and control signals. Some reference designs are shown below as well.

### 3.2.2.1 UART Signals

There is a communication between OPS PC and the docking board via UART signals. Designer can communicate with the OPS PC by using these signals. The specification of the UART signals can be seen in Table 3.3 below.

| Pin No | Name     | Туре | Description                                                                                                                         |

|--------|----------|------|-------------------------------------------------------------------------------------------------------------------------------------|

| 52     | UART_TXD | 0    | Transmitted UART data from pluggable board, UART<br>3.3V LVTTL signal. Assign as COM 1 for the UART port<br>in the pluggable module |

| 51     | UART_RXD | Ι    | Received UART data for pluggable board, UART 3.3V<br>LVTTL signal. Assign as COM 1 for the UART port in the<br>pluggable module     |

Table 3.3 OPS PC UART signals

### 3.2.2.2 Control Signals

There are some control signals that designer can control the OPS PC by using these signals. By the help of these signals, designer can understand the existence of the OPS PC and can power ON or OFF the OPS PC. The specification of the control signals can be seen in Table 3.4 below.

Table 3.4 Control signals of OPS

| Pin No | Name       | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 74     | PWR_STATUS | OC   | Power status indication signal or Power Good status of<br>the pluggable board. This pin shall be Open Collector<br>and pull up to +3.3V on the docking/control board side.                                                                                                                                                                                                                            |

|        |            |      | High: Pluggable board power off state<br>Low: Pluggable board power on state                                                                                                                                                                                                                                                                                                                          |

| 73     | PS_ON#     | Ι    | <ul> <li>Pluggable Signal ON: This is meant for signal initiation to power ON or boot up the Pluggable Module. PS_ON# shall be asserted at least 500ms after power is delivered from PSU to the board via the JAE connector (G3 to S5 state). Pull up to +3.3V on the pluggable board.</li> <li>A pulse width present on the PS_ON# shall be detected and responded within 200ms to ensure</li> </ul> |

|        |            |      | detected and responded within 200ms to ensure successful operation.                                                                                                                                                                                                                                                                                                                                   |

| 72     | PB_DET     | 0    | Pluggable board detection. Output signal, recommend<br>rounded on the pluggable board side with pull up to<br>+3.3V on the docking/control board side<br>High:No Pluggable<br>Low: Pluggable board Present                                                                                                                                                                                            |

| 71     | CEC        | I/O  | Consumer Electronics Control for Proof of Play/Display<br>initiative. Can also be used for display panel status<br>detection and other control functions. The display panel<br>control CPU shall support this functionality.                                                                                                                                                                          |

| 50     | SYS_FAN    | 0    | System Fan: This signal shall be used to control the<br>display panel system fan. Recommended pull up +3.3V<br>on docking board side and routed to the system fan<br>control.<br>High: System Fan OFF<br>Low: System Fan ON                                                                                                                                                                           |

Figure 3.16 Reference design example for PWR\_STATUS

Figure 3.17 Reference design example for PS\_ON#

Figure 3.18 Reference design example for PB\_DET

For control signals, some special circuits according to the OPS specification need to be designed. These special circuits can be seen in Figure 3.16, 3.17 and 3.18 above respectively.

Figure 3.19 OPS PC mainboard top view

Figure 3.20 OPS PC mainboard bottom view

Figure 3.21 OPS PC mechanical dimensions (NEC)

#### **3.3 SMPS Power Supply**

In this product, a 300W output capable SMPS power supply is used. SMPS power supply has different types of voltages as outputs such as DC24V for backlight and audio amplification, DC12V for system supply and also has some control signals such as backlight on/off and standby on/off.

The power board includes AC-DC resonant half bridge converter and DC-DC converter. This PSU has active PFC (Power Factor Correction) unit. Total max output power is 300W. Stand by power consumption is under 0.5W when 13Vstby-15mA @AC 220V and other outputs have no load.

The input specifications and currents can be drawn from each outputs are listed below in Table 3.5 and Table 3.6 respectively.

Table 3.5 Input specifications of the power board

| Standard Voltage Range | AC 220V-240V |

|------------------------|--------------|

| Maximum Voltage Range  | AC 100V-264V |

| Frequency Range        | 50Hz - 60Hz  |

| CH# | Output Name | Output  | Variable        | Voltage | Output Current (mA) |         |

|-----|-------------|---------|-----------------|---------|---------------------|---------|

|     |             | Typical | Typical Voltage |         | Minimum             | Maximum |

|     |             | (V)     | Range (V)       | (%)     |                     |         |

| CH1 | +13V_STBY   | 13      | 12.5 - 13.5     | ±3      | 10                  | 400     |

| CH2 | 3.3V        | 3.4     | 3.3 - 3.45      | ±3      | 30                  | 2500    |

| CH3 | 5V          | 5.1     | 4.95 - 5.15     | ±3      | 30                  | 2500    |

| CH4 | 12V         | 11.8    | 11.5 – 12.3     | ±3      | 500                 | 6000    |

| CH5 | 24V         | 24      | 23.7 - 24.4     | ±3      | 1000                | 10000   |

| CH6 | 24V_PL806   | 24      | 23.5 - 24.2     | ±3      | 0                   | 1000    |

| CH7 | +18V_A      | 18.5    | 17 - 19         | ±3      | 0                   | 1000    |

Table 3.6 Output specifications of the power board

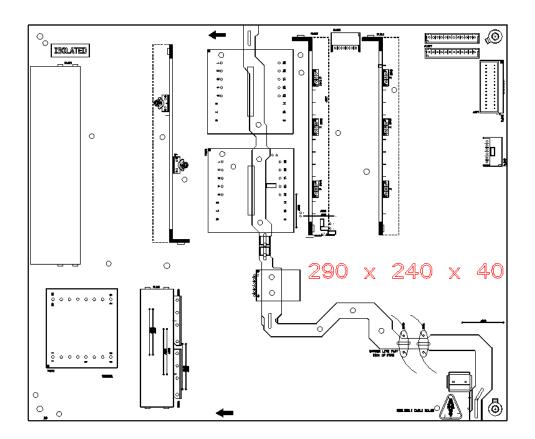

Figure 3.22 Drawing of the SMPS power board

Figure 3.23 Power board top view

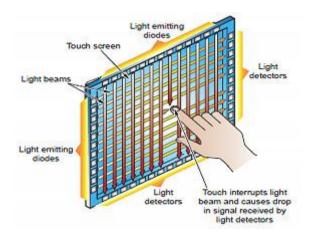

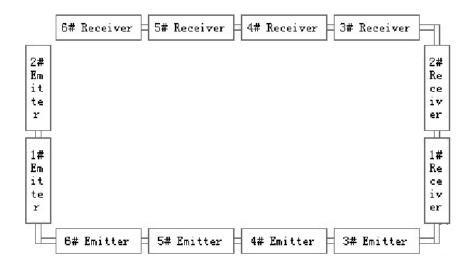

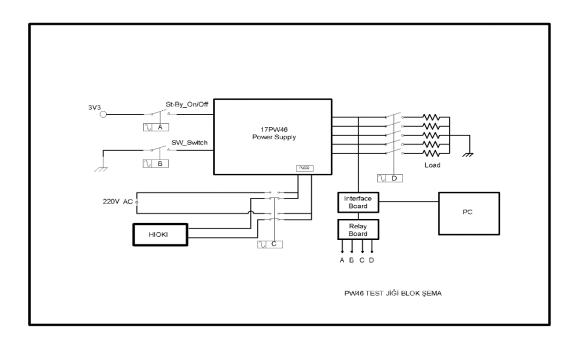

## 3.4 I/R Touch Screen